阚子杨 刘萧鸣 赵鹤煜 涂振华 孙赫阳 姜绍君

关键词:FPGA;Verilog HDL;Quartus II;计时器

中图分类号:TP311 文献标识码:B

文章编号:1009-3044(2023)12-0089-03

可控计时器在日常生活中有着广泛的应用,例如交通灯信号控制,竞赛倒计时,考试计时器等各个方面,如何快速准确计时,且不出现误差,就需要通过精确的仪器来计时。基于FPGA的硬件逻辑编程语言实现计时器设计,可以准确地进行30秒的计时功能并显示,减少人类短时计时的时间误差。

1 设计

1.1 实现功能

1) 具有30秒计时,显示功能,计时间隔为1秒。

2) 调整外部开关,控制计时器直接清零,装数,启动和保持(暂停)功能。

3) 计时器递减到0时候显示器不能灭灯,同时发出报警信号(报警灯亮起)。

4) 能够解除警报。

5) 引脚说明:

输入信号:时钟CPA、直接清零CR、预置LD及减计数使能S。

输出信号:QH[3..0]、QL[3..0](余3码)和报警信号L。

1.2 原理

1.2.1 设计基础

FPGA(Field Programmable Gate Array) ,完整形式是现场可编程逻辑门阵列,是一种电子设备,用于执行任何(数字)逻辑功能或数字电路的硬件实现;是在传统逻辑电路和门阵列PAL、GAL,CPLD等可编程器件的基础上进一步发展的产物[1]。FPGA最大的特点是它们是现场可编程的,这意味着它们在制造出来后,可以由客户根据自己的要求在现场重新编程,优点是可重复编程且低功耗。

Verilog HDL 是一种硬件描述语言,语法与C 接近,但Verilog语言是硬件设计语言,与C实质不同,用于多层次的数字系统建模,代码对应硬件实体[2]。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Quartus,是Altera公司推出的综合性CPLD/FPGA开发设计软件,一种可编程逻辑的开发设计环境,软件支持原理图、VHDL、Verilong HDL等多种输入形式,以及自带仿真器,可以进行波形,原理图以及顶层文件等设计绘制和仿真,可以完成从设计输入到硬件配置的完整PLD设计流程。(——引用于百度百科词条)

DE2_115开发板,核心是FPGA芯片,存储芯片3 种,IO口配置分别为4个按钮,18个开关,18个RED- LED,9个GREEN-LED,8个七段数码管,32字符液晶显示屏;且含有标准接口:通用串行总线USB控制模块以及A、B型接口,2个以太网络适配器,RS-232标准串口,PS/2键盘接口;其他:50M晶振,支持外部时钟,外接IO,1个连接器[3]。

1.2.2 设计原理

系统的核心部分是30秒可控递减计时器,由外部开关按键进行清零(CR) ,直接控制递减计时器的复位以及解除报警;预置键LD=0有效,当可控计时器调至30秒时,输出信号高四位QH[3..0]和低四位QL[3..0]分别为0110、0011(余3码),说明可控计时器实现了置数功能;S为启动和保持(暂停)按键,当S=1时用于递减计时器启动时,当S=0时用于保持(暂停)[4]。

2 总体设计

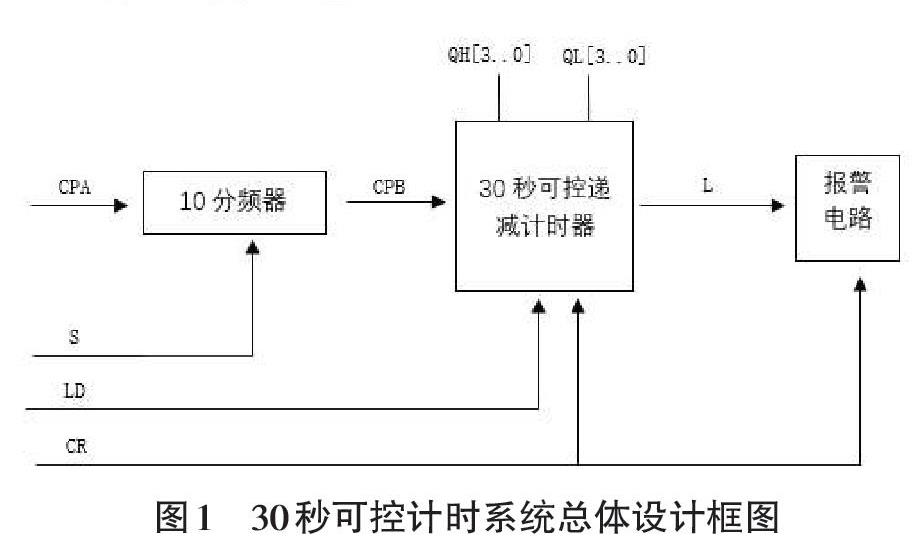

总体设计框图,如图1所示。

框图包括10分频器,30秒可控递减计时器及报警电路。30秒可控递减计时器是整个系统的核心部分,S=0时候用于暂停或者保持,S=1时候正常使用;当输入清零信号(CR) =1,可以直接控制递减计时器的复位和接触报警(L=0) 功能;一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率较高)进行分频,框图中的分频器的功能是为了对多种频率进行分频,提高控制精度,减小时间计时误差。

3 硬件设计

3.1 框图顶层文件

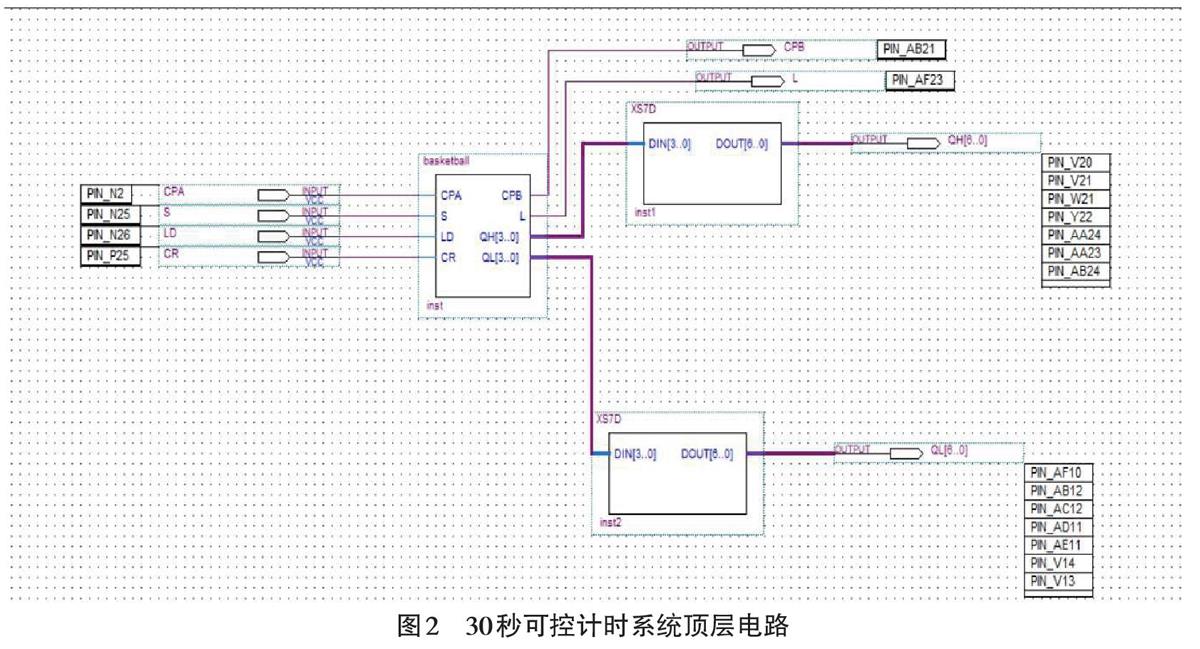

设计遵循最优解原则,将代码极简,输入,分频,显示,控制函数都编程在一个工程文件下,再建立顶层文件放在一个目录下,画图编辑,建立Vector Wave? form file进行实验仿真[5]。框图顶层文件,如图2所示。

3.2 模块设计

分频器和30可控递减计时器模块主要实现的是数字从30秒开始每秒进行减一的功能,首先拨动CR 清零后,就可以直接启动分频已经计时功能,数字将会在30秒递减,也可以时间暂停和开始等功能。

显示器模块主要是显示30秒的递减的实现结果,当与之相对应的快关拨动时,可以在显示器上看到数字的跳动、停止和重置等功能。

笔者在这里选择使用DE2_115 开发板进行仿真。在DE2_115 开发板上进行仿真,可以更加直观地观测实物。其中分频器使用的是开发板自带的晶振分频,数字显示模块使用的是两位八段译码管,控制模块则使用触发开关,其余功能使用发光二极管表示。

4 仿真

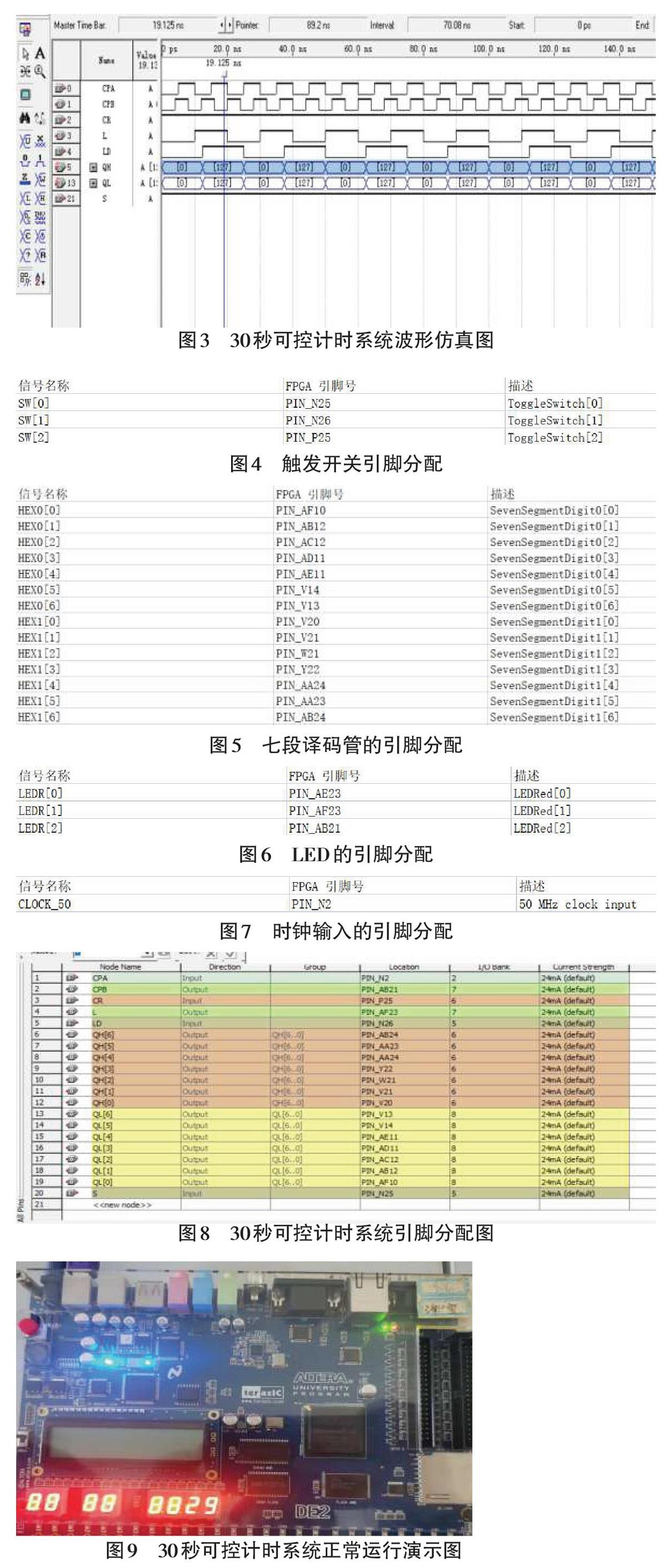

CPA为时钟定时50MHz,S为启动暂停,CR为清零,S设置为高电平代表为启动,整个电路继续进行CR为高电平跳变触发,CPA、CPB设置时钟频率[5],当暂停、清零以及数字30秒时L为报警电路跳变为高电平,对应的发光二极管开始工作。

为了测试计时器的功能是否正常,我们可以控制S=0或者1,来观察可控计时器能否正常递减计数,当计数器递减至0的时候能否发出报警信号L是否为1。当输入清零(CR)低电平信号时,直接复位并解除报警,实现功能。

其仿真图如图3所示。

通过仿真波形图可以看出,当30秒可控计时器正常运行时,预置按键LD=0有效,当计时器调为30秒时,输出信号高四位QH[3..0]和低四位QL[3..0]分别为0110、0011(余3码),即实现置数功能;启动和保持(暂停)按键为S,当S=1高电平的时,用于递减计(启动)时,当S=0低电平时用于保持(暂停)[6]。

5 下载验证

本次使用DE2_115开发板进行下载仿真验证,各位读者可以进行参考本次验证,由于实验的偶然性,本次实验不排除有错误的情况。

首先使用Quartus||软件中的Assignments—pins功能为工程图分配管脚,此处附上管脚分配图如图4~图7所示。

CPA分配表D.4.1时钟输入的引脚分配CLOCK_50;S、CP、LD分配表D.1.1触发丌关引脚分配SW[0]、SW[1]、SW[2];L、CPB分配表D.1.3LED的引脚分配LEDR[0]、LEDR[1];QL[6..0]分配表D.1.9七段数据管的引脚HEX[0-6]; QH[6..0]分配表HEX1[0-6],如图8所示。

使用USB数据线和电源线连接开发板,再使用软件的Programmer功能Hardware Setup,将Currently se? lected hardware 搜索USB数据线配置,最后点击start 进行下载,最后在开发板上进行验证操作。

演示验证状态如下所示:实现了以下功能:

1)具有30秒计时,显示功能,计时间隔为1秒,如图9所示。

2)计时器递减到0时候显示器不能灭灯,同时发出报警信号(报警灯亮起),如图10 所示。

3)调整外部开关,控制计时器直接清零,装数,启动和保持(暂停)功能,如图11所示。

6 总结

本文采用了分块设计的思想设计了简单计时器,通过对FPGA的了解学习,进一步熟悉和掌握了Quartus II软件的使用方法,现能够利用Verilog HDL 语言设计简单数字电路系统,本文分别设计了分频模块,递减计时模块,报警模块,且通过软件进行波形仿真对比,对结果进行验证。经过反复修改与验证后,最终实现了所需功能,使30秒可控计时器能够正常使用。