惠为君

摘要:SOC内部总线用于连接其内部的各个部件,实现主控部件与从属部件等的数据传输,是SOC设计必不可少的关键部件。本文分析了SOC总线特性、结构,对系统进行了模块划分。在设计了仲裁协议的基础上,基于quartus平台,verilogHDL语言实现了各模块的设计。Modelsim仿真和FPGA下载验证表明,设计是有效的。

关键词:总线;Verilog HDL;Modelsim;FPGA

中图分类号:TN91 文献标识码: A

文章编号:1009-3044(2021)14-0206-02

总线是SOC系统中CPU与内存、IO设备之间的共享通道。内部总线的设计往往决定了芯片的性能、时延及芯片的复杂度。SOC内部总线一般具有数据传送并行、连接部件多、全双工通信的特点。

连接总线的部件分为主控部件和从属部件。主控部件向总线申请,总线经过仲裁,批准了该主控部件的使用权,同时向从属部件发出片选信号,在此基础上,主控部件与从属部件通过总线实现数据传输。

1信号定义

主控部件、总线、从属部件通信的信号定义如图1所示。

主控部件和从属部件挂在总线上,通过总线进行通信,二者不直接有引脚连接。从图1可以看出,主控部件和从属部件通过总线实现全双工并行通信,读写分开,提高了效率。

总线可以挂接若干主控部件和从属部件。每个主控部件定义了7种引脚,引脚名称、宽度等定义如表1所示。

从属部件定义了5种引脚,引脚名称、宽度等定义如表2所示。

2 总体设计

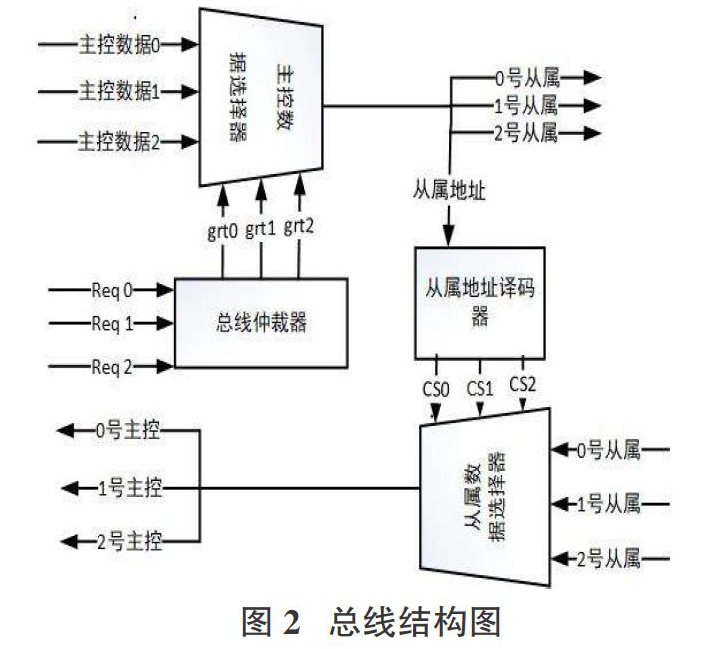

从功能上划分,总线结构分为四个部分,如图2所示。为简单计,主控部件和从属部件都取三个。

按照功能划分,总线结构分为如下四个部分。

1)主控数据选择器:根据仲裁结果,选择一个主控部件。

2)总线仲裁器:根据总裁机制,选择一个主控部件拥有总线使用权。

3)地址译码器:主控部件输出从属部件地址,译码器根据地址生成从属部件的片选信号。

4)从属数据选择器:根据片选信号,选择一个从属部件。

3 模块设计

总线仲裁器决定和一个主控部件通信的从属部件。主控部件向仲裁器发出请求信号(req),仲裁器根据仲裁机制,发出有效的批准信号(grt),授予一个主控部件总线使用权。

三个主控部件没有优先级,随机向总线申请使用权。仲裁器采用轮询作为仲裁机制,按照请求的先后顺序确定总线使用权。仲裁器是一种周期动作的模块电路,使用状态机来设计。对应主控部件数,设计三个状态。

1)状态0:0号主控部件取得总线使用权。

2)状态1:1号主控部件取得总线使用权。

3)状态2:2号主控部件取得总线使用权。

在状态0时,也就是0号主控部件使用总线的时候,主控部件请求被批准的顺序为0号1号2号。依次类推,状态1时,批准顺序为1号 2号 0号,状态2时,批准顺序为2号0号1号。 其状态转换图如图2所示。Req0、Req1和Req2为三个主控部件向总线申请使用权信号,其值为1时,表示申请使用权,为0时,表示撤销申请使用权。

复位及默认状态时,系统的状态取状态0。

3.1 主控数据选择器

接受一个主控部件的Addr、Rw、Addr_s、Wr_data信号。其中,Addr信号发给从属地址译码器,其余信号发给从属部件。

4 模块实现及仿真

基于Verilog HDl实现各模块。模块的文件名,如表3所示。

4.1 总线仲裁器

实现仲裁控制的部分核心代码如下:

case(owner)

2'b00 : begin

if(req0 == 1'b1) owner = 2'b00;

else if(req1 == 1'b1) owner = 2'b01;

else if(req2==1'b1) owner = 2'b10; end

2'b01 : begin

if(req1 == 1'b1) owner = 2'b01;

else if(req2 == 1'b1) owner = 2'b10;

else if(req0 == 1'b1) owner = 2'b00; end

2'b10 : begin

if(req2 == 1'b1) owner = 2'b10;

else if(req0 == 1'b1) owner = 2'b00;

else if(req1 == 1'b1) owner = 2'b01; end

default: owner = 2'b00;

模块用一个摩尔状态机来实现,按照仲裁器状态图实现状态机代码。寄存器owner存储轮询状态,在时钟的触发下,不同的状态授权不同的主控模块取得总线使用权。

4.2 总线顶层模块

实现了各模块之后,按照图2总线结构图,实例化个模块,完成总线设计。 实例化模块部分代码如下:

bus_arbiter u2(.clk(clk),.reset(reset),.req0(req0),.req1(req1),.req2(req2),.grant0(tgrant0),.grant1(tgrant1),.grant2(tgrant2));

bus_slave_addr_dec u3(.slave_addr(tslave_addr),.cs0(tcs0),.cs1(tcs1),.cs2(tcs2)) ;

模块实现的symbol如图4所示。输入部分只显示了一个主控部件信号,其余信号可以类推。

4.3 总线模块仿真

基于modelsim对顶层模块bus进行了仿真。仿真结果如图5所示,可以看出,主控部件和从属部件的数目都取三个,总线输出mdata和sdata的读取是正确的。

5结束语

对SOC内部总线的特征进行了分析,在此基础上,按照不同的功能进行了模块划分。划分的四个模块分别是总线仲裁器、主控部件数据选择器、从属部件数据选择器、从属部件地址译码器。在分析了仲裁协议的基础上,利用状态机技术完成了仲裁器设计。完成了四个模块设计以后,利用模块实例化方法实现了顶层模块设计。为了试验方便,本设计采用了较少的主控部件和从属部件数目,在这一方面,设计还可以改善。

【通联编辑:梁书】