龚泉铭+姜秀杰+安军社

摘 要: 为了实现一种适用于航天应用的星载存储方案,给出一个基于FPGA实现的星载简易复接存储器设计。该存储器可以完成航天应用的大容量数据缓存工作。其中前端仲裁部分采用依据数据量大小而设置的不同优先级,保证数据完整地完成复接任务。同时,提出一种自刷新和自动刷新协同工作的刷新控制机制和新的地址指针分配方式,使得大容量存储系统的存储数据无误差、无丢失,读写正常有序的数据。经板级验证,该方案整体可以实现的最高存储速率可达1 Gbit/s。

关键词: 星载存储器; SDRAM; 刷新机制; 航天应用; FPGA实现; 大容量数据缓存

中图分类号: TN919.3?34; TP333 文献标识码: A 文章编号: 1004?373X(2018)06?0065?05

Abstract: A spaceborne storage scheme suitable for aerospace application is achieved. Design of a simple spaceborne multiplexed memory based on FPGA realization is given. The memory can accomplish large?capacity data cache work in aerospace application. For the front?end arbitration part, different priorities which are set according to the size of data quantity are adopted to achieve the multiplex task with data integrity guaranteed. A refresh control mechanism with cooperative working of self?refresh and auto refresh and a new address pointer allocation mode are proposed to ensure that no storage data error or loss exists in the large?capacity storage system and data can be read or written properly and orderly. Board?level verification shows that the scheme as a whole can realize a maximum storage rate of 1 Gbit/s.

Keywords: spaceborne memory; SDRAM; refresh mechanism; aerospace application; FPGA realization; large?capacity data cache

0 引 言

在航天领域中,空间飞行器在运行过程中会进行各种科学数据的采集,并且将采集到的数据存放在空间飞行器的数据存储设备中,并在适当的时候将数据下传地面,以供科技工作者分析使用。在整个任务运行过程当中,数据存储设备起到了重要的数据缓存作用。同样的,星载图像处理系统中,在数据的采集和显示环节需要实现大量数据的快速访问,因而也需要大容量高速度的存储设备进行数据存储。而SDRAM所具有的容量大、速度快、价格低的特点,以及较低的功耗[1],使其在现今的星载存储器中占有重要地位。

现有的SDRAM控制器实现相对较好的瞬时数据吞吐率,能够满足视频数据的处理需求的控制器,例如文献[2]所设计的视频解码器的高性能SDRAM 控制器。为了优化刷新性能,部分控制器开展了对SDRAM刷新机制的研究,例如文献[3]中提出通过读写进程与刷新进程的交替机制,使得用户在进行全页突发写或者突发读时不考虑SDRAM 刷新请求,在一定程度上优化了对SDRAM的操作。

目前对刷新的优化方法结合两种刷新模式的特点,主要分为两种:集中式刷新机制和分布式刷新机制。集中式刷新机制,即在64 ms内一次性完成8 192次自动刷新操作,一次性完成刷新后,在剩余的时间可全部用来完成SDRAM的数据吞吐工作。分布式刷新机制则是每7.8 ms进行一次自动刷新操作,通过自动刷新将64 ms划分为8 192个时间片段,SDRAM的数据吞吐全部在时间片段中完成[4]。但面对航天应用的特殊环境缺乏有针对性的控制器设计方法。本文通过对自刷新和自动刷新在不同场合的合理应用,读地址和写地址的合理划分来进一步提高控制器在多路数据复用情况下,实现一种数据高效、稳定、低功耗传输的SDRAM星载存储控制器。

1 总体结构划分

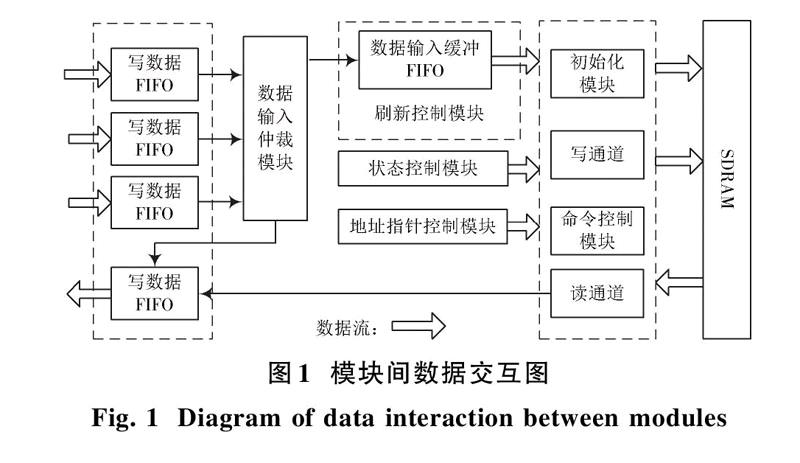

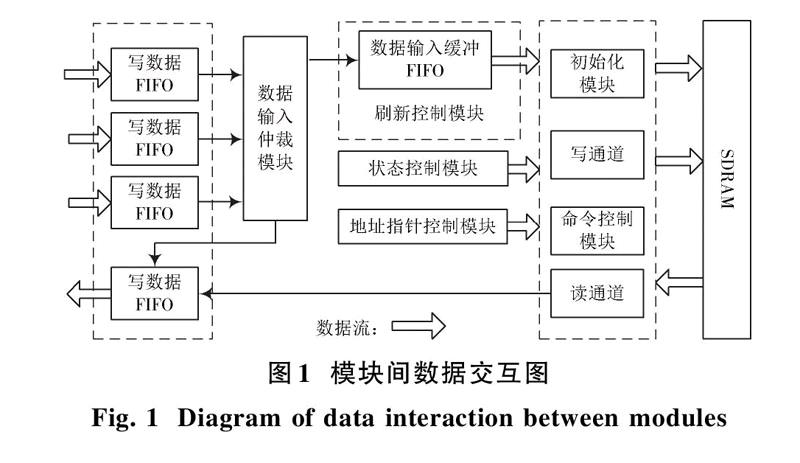

SDRAM存储控制器主要模块包括:输入数据缓存模块、仲裁模块、状态转换控制模块、地址指针控制模块和主控制器五部分,如图1所示。其中输入数据缓存模块和仲裁模块,用于缓存多路输入数据,并进行轮询仲裁后,输出给后端模块;状态控制模块用于产生各类SDRAM控制命令;地址指针控制模块对片选信号、Bank信号、行地址信号和列地址信号进行管理,并配合读/写命令输出相应地址。

主控制器完成对SDRAM的直接命令控制,工作时钟为48 MHz,其中包含的初始化模块,负责执行SDRAM上电后的初始化;仲裁模块用于对三组输入数据的优先级仲裁;状态转换控制模块用于对SDRAM的写操作、读操作、自刷新操作和自动刷新操作的控制和转换;地址指针控制模块用于对SDRAM的片选、Bank、行地址和列地址的控制和写入。读通道则根据系统运行状态,在无数据写入请求的情况下将数据读出,进行相应转换(如并串转换),然后下传数据。

2 存储器地址指针设计

对于512 M×8 bit SDRAM的芯片,其地址空间为512 MB,其中列地址为12位,行地址为13位,Bank为2位,片选[5?6]为2位。数据在由数据源输入控制器前,已完成相应格式源包大小为512 B的打包操作。依据这一特性,可以将地址空间分成两大部分:一部分由28~10位组成数据包的地址,另一部分由9~0位组成数据包内的数据地址,如图2所示。

在对地址指针进行控制时,将地址指针分到两个模块进行控制:在处理控制模块中,每收到一整包数据后数据包地址加1,指针信息以包计数的方式表示,即0x00000~0xFFFFF,方便与CPU模块进行地址信息交互,不涉及包内数据地址信息;由于SDRAM写入或读出包数据对数据包地址没有影响,因此在SDRAM控制模块只对包内数据地址进行处理,即结合突发读/写操作,每次给SDRAM写入一个地址后,完成8×8 bit的数据读/写。每完成一整包数据的读/写,包内数据地址完成一次循环。

地址指针的区分,可以将对数据的操作区分为整包操作和包内数据的读写操作两部分,从而方便后面结合刷新机制的控制模式的优化和实现。

3 存储器协同刷新机制设计

3.1 刷新模式的工作特点

每一种动态存储器都需要在一定的时间间隔内进行刷新(Refresh)操作来保证存储器内数据的正确性,SDRAM 也不例外。刷新计数器决定了刷新的时间间隔,从而保证存储器的每个单元都能进行周期性刷新。SDRAM芯片本身提供了两种类型的刷新模式:自动刷新(Auto Refresh)和自刷新(Self?Refresh)。在SDRAM控制器的设计中,一些通用为简化设计通常只会采用一种刷新方式,这样可以尽量简化控制过程,使控制器的操作更为简单。目前一般常用电容式存储体中电容的数据有效保存期上限是64 ms,即每一行刷新的循环周期是64 ms。这样刷新周期就是每Bank中的行数量为64 ms,所以SDRAM芯片的行数量越多,需要刷新的周期就越短。

自动刷新模式:由于刷新命令一次只对一行有效,发送间隔也是随一个Bank中所具有的行数的变化而变化的。如若一个Bank中包含4 096行时,刷新周期为64 ms/4 096=15.625 μs。文本设计使用的SDRAM包含8 192行,因此其刷新间隔为[64 ms8 192]=7 812.5 ns。譬如,时钟周期为120 MHz,周期为[1120×106=8.3 ns],因此,[7 8128.3=941,]即每隔941个时钟周期需要给一个刷新控制指令。考虑到其他操作的时间,一般取值会小于941,从而满足刷新周期的要求。

自刷新模式:主要用于休眠模式低功耗状态下的数据保存,在发出自刷新命令时,将时钟使能CKE置于无效状态进入自刷新模式,此时不再依靠系统时钟工作, 而是根据内部的时钟进行刷新操作[4]。由于无需系统时钟控制,但有单独的进入自刷新和退出自刷新操作命令,未避免多次发送进入/退出自刷新命令的繁琐操作,需要每64 ms抽出一个时间段,来对8 192行数据进行一次性的刷新操作。

考虑到自刷新和自动刷新在使用过程都各自有其优势,单独使用其中任何一种方式均不能充分发挥每种刷新模式的特点和优势,同时无法达到高可靠和低功耗的设计目的。下面,主要介绍一种刷新方式协同工作的存储控制器。

3.2 刷新方式的计算方法

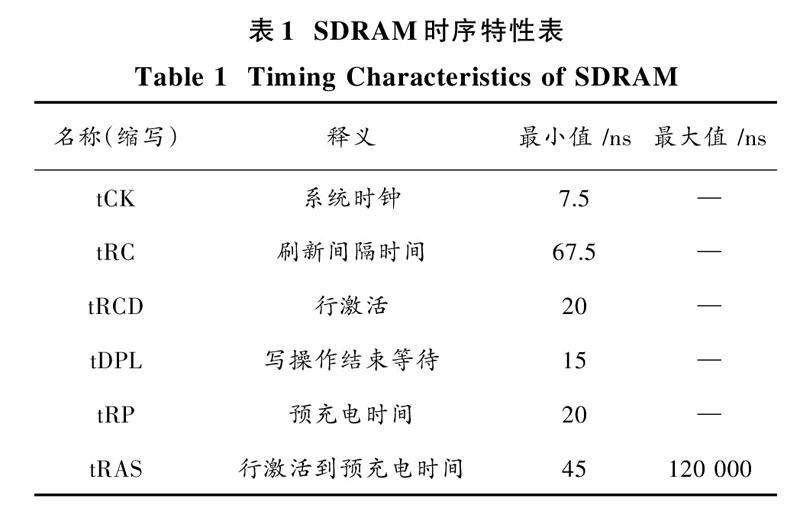

对于协同工作的刷新机制,需要很好地分配两种刷新模式的工作时机和次数。为此需先了解SDRAM各种基本的操作方式:空操作(NOP)、行激活操作(ACTIVE)、突发写(BurstWrite)、突发读(Burst Read)、自动刷新(Auto Refresh)、自刷新(Self?Refresh)、预充电(Precharge)和模式寄存器配置(Mode Register Set)等[7]。所有的操作命令都通过信号线CS,RAS,CAS和WE共同控制。不同的操作都有相应的时间要求,SDRAM时序特性表如表1所示。

除了了解以上操作方式外,还需了解数据源产生数据的特点,本设计中使用的数据源产生数据的方式如图3所示。数据源1输出1帧的科学数据的时间为0.29 s,其大小为131 120 B,通过打包模块分成261个数据源包;数据源2与数据源3类似,1帧科学数据的大小为5 086 276 B,传输时间为1.02 s,组合成数据源包数量为10 133包。数据流将数据源包匀速发送到缓存控制模块的接收FIFO中。

由于SDRAM需要在64 ms内完成8 192次的自动刷新操作,为了方便分析,将整个传输过程以64 ms为时间片段,划分为若干个时隙。为此,需计算每个时隙中三路数据源传输的数据包数量的和作为时隙传输的最大传输量。其计算方式为:

[一帧数据传输时间该时间内传输源包数量=64N] (1)

将三路数据源代入式(1),如下:

[290261=64N1] (2)

[1.0210 133=64N2] (3)

[1.0210 133=64N3] (4)

式中,[Ni](i=1,2,3)为数据源i在64 ms内到达的源包数量,计算结果如下:

[N1≈58,N2=N3≈649]

所以,每64 ms的时隙内,接收了[N1+N2+N3≈1 356]个源包的数据。因此,每一个数据源包完成读写操作后,需要完成的自动刷新次数为[8 1921 356≈6]。即在每次读/写操作后,自动跳入6次自动刷新状态,这样能保证在达到最大传输速率时,SDRAM依然能完成64 ms内8 192次的刷新操作,从而保证存储单元上的数据不丢失。在无读/写任务情况下,SDRAM会进入自刷新状态,能很好补偿由于读/写次数减少而减少的自动刷新次数,进而保证64 ms足够的刷新次数。存储控制器的状态转化过程如图4所示。对于一个使用协同刷新机制的SDRAM存储控制器而言,当系统时钟为48 MHz,传输数据源包大小为512时, SDRAM完成一次数据包读/写操作后,再进行6次自动刷新操作,即可在64 ms的规定时间内完成足够次数的自动刷新操作,保证SDRAM在数据传输和存储过程中数据不会出现异常或丢失。

4 验证与分析

4.1 刷新功能的能耗分析

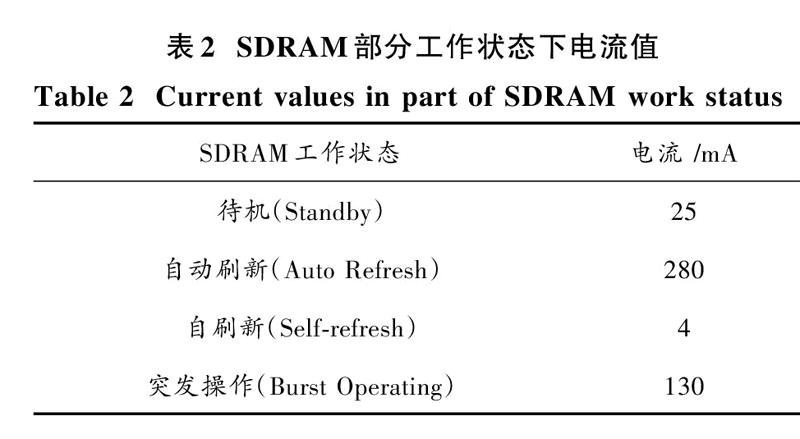

在实际的航天任务中,端口数据量大小具有随机性,SDRAM的读/写操作会使SDRAM处于不同的工作状态,而不同的工作状态所消耗的能量不同,即不同工作状态下的电流大小不同,如表2所示。

由第3.2节可知,当存储控制器工作在满负荷状态,即三路数据源均发送数据时,本文设计的控制器能很好地完成SDRAM芯片所需的刷新任务要求。当控制器未处于满负荷状态时,相比一般控制器的待机模式,自刷新模式既完成了SDRAM刷新任务的要求,又能实现低功耗的运行,从而实现高可靠存储与低功耗的运行的兼容。

4.2 软件仿真验证

该设计的软件功能仿真是利用硬件描述语言VHDL写出测试代码,在Mentor公司的ModelSim软件中进行,通过检查波形完成。仿真条件:时钟为48 MHz,复位信号高有效并持续100 ns;写入512 B 的数据,采用突发长度(Burst Length)为8,将数据通过连续64次突发操作写入SDRAM 中,然后再将写入的数据在突发长度8的条件下读出。经过Modelsim功能仿真的波形如图5所示。结果表明该设计能顺利地完成读写、刷新和预充电,行与行、块与块之间的交换平稳迅速,无论是连续还是单个操作都非常顺畅。一次整包的读操作或写操作都通过64次Burst完成,总共完成一整包512 B数据传输及相应的自动刷新和自刷新操作。

4.3 FPGA验证

该设计的硬件验证在Xilinx公司的Virtex?4系列的芯片中进行,通过三个数据源输入相应数据流,对存储控制器输出的数据进行解析,如图6所示。并与数据源数据进行比对,确认输出的数据与数据源数据完全吻合。

综上,基础逻辑单元资源占用率为3%,引脚资源占用率为17%,最大工作频率为174.619 MHz,远远大于SDRAM芯片最大工作频率133 MHz,实现了峰值传输速率1 Gbit/s,满足设计要求并已成功在某航天型号任务中作为大容量数据缓存使用,经过一系列环境模拟实验均工作正常,满足航天相关应用需求。

5 结 语

本文依据航天应用的特点,结合现有存储控制器的使用特点,提出一种地址指针合理分配和优化的刷新方式,即自刷新和自动刷新协同工作的刷新方式,提高了单位时间内SDRAM的读/写速率,通过将刷新操作碎片化到每一次读写操作中,在保证数据正确传输的基础上又提高了传输的连续性。通过前端输入数据仲裁机制和后端两种刷新协同工作的设计,满足了航天应用中对星载设备高效、稳定和低功耗的综合需求。同时结合了FPGA高效、并行等优势,使得该设计方案对SDRAM的实际使用中性能的改善和以后的复接存储器的设计提供参考。

参考文献

[1] LEE D, KIM Y, SESHADRI V, et al. Tiered?latency DRAM: a low latency and low cost DRAM architecture [C]// Proceedings of IEEE International Symposium on High Performance Computer Architecture. Shenzhen: IEEE, 2013: 615?626.

[2] 高战立,余桂英,唐玮.FPGA图像采集系统研究与设计[J].中国计量学院学报,2014,25(1):75?79.

GAO Zhanli, YU Guiying, TANG Wei. Research and design of an image acquisition system based on FPGA [J]. Journal of China University of Metrology, 2014, 25(1): 75?79.

[3] 张林,何春.高速SDRAM控制器设计的FPGA实现[J].电子科技大学学报,2008,37(z1):109?112.

ZHANG Lin, HE Chun. FPGA implementation of high speed SDRAM controller [J]. Journal of University of Electronic Science and Technology of China, 2008, 37(S1): 109?112.

[4] 金新强,白雪飞,张璠.一种DDR SDRAM控制器的设计[J].微型机与应用,2013,32(8):23?25.

JIN Xinqiang, BAI Xuefei, ZHANG Fan. Design of a DDR SDRAM controller [J]. Microcomputer & its applications, 2013, 32(8): 23?25.

[5] Micron Technology Inc. 8Gbit SDRAM EDS5104AB datasheet [EB/OL]. [2003?01?10]. http://www.elpida.com.

[6] Micron Technology Inc. General DDR SDRAM functionality [EB/OL]. [2013?01?13]. http://www.micron.com.

[7] 陈瑞斌,唐惠玲,徐虎,等.基于FPGA的页快速命中的SDRAM控制器的设计[J].现代电子技术,2015,38(13):63?66.

CHEN Ruibin, TANG Huiling, Xu Hu, et al. Design for FPGA?based SDRAM controller of page fast hitting [J]. Modern electronics technique, 2015, 38(13): 63?66.

[8] 于跃忠,黄振,林孝康.SDRAM文件结构存储控制的FPGA实现[J].现代电子技术,2010,33(14):167?170.

YU Yuezhong, HUANG Zhen, LIN Xiaokang. FPGA implementation of file structure storage control for SDRAM [J]. Modern electronics technique, 2010, 33(14): 167?170.

[9] 王宏,张旭炜,胡挺,等.光纤传感系统SDRAM控制器的FPGA设计与实现[J].光通信技术,2013,37(1):41?43.

WANG Hong, ZHANG Xuwei, HU Ting, et al. Design and realization of the SDRAM controller based on FPGA used in fiber sensor system [J]. Optical communication technology, 2013, 37(1): 41?43.

[10] 赵传猛,高岩,张蓉.一种简单的SDRAM控制器实现[J].计算机与数字工程,2010,38(8):197?200.

ZHAO Chuanmeng, GAO Yan, ZHANG Rong. A simple design and implementation of SDRAM controller [J]. Computer and digital engineering, 2010, 38(8): 197?200.