于洪洲,徐叔喜,沈吉

(中国兵器工业第214研究所,江苏苏州, 215163)

0 引言

在日常生活中由于静电现象无处不在,时时刻刻对电子电路产品产生严重威胁和可能的破坏,所以ESD保护是每一个电子产品必不可少的部分,虽然目前的半导体集成电路内部均设计了ESD保护单元,但是只能抵抗一部分能量较低的ESD静电破坏,大部分的抗ESD静电破坏的任务还需要交给专门的ESD保护器件来完成。

ESD保护器件主要安放在电子产品PCB印制板的端口处,比如电源端的输入和输出端口、执行器的驱动电路的输出端口、传感器的输入端口,以及数据通讯的连接端口等。针对不同的连接端口和其传输信号的特点,需要选取不同的ESD保护器件或者组合,来进行ESD静电防护。

为了满足USB接口等高速数据通讯端口的抗静电保护需要,设计一款双通道抗静电保护电路。电路原理图见图1所示,电路提供两个静电保护端口D+和D-,图中T1为普通TVS管,虽然抗静电效果好,但是其结电容比较大,一般在十几pF到几十pF之间,严重影响被保护器件的通讯速度,在这里我们采用串并联低电容二极管的方式解决这个问题,也就是图中的二极管D1和D2,这两个二极管的结电容设计值一般在0.5pF以下。D1提供反向静电泄放通道,D2和静电击穿后的T1串联提供正向静电泄放通道。这样端口电容可以降低到1pF以下,既保证提供良好的抗静电效果,又不会影响被保护器件的高速数据通讯功能。另外,为了减小封装时芯片硅铝丝到管脚的寄生电容,电路采用SOT-23塑料封装。

图1 电路原理图

1 性能指标

电路主要技术指标主要有三个,如下:

(1)IO端口电流:≤0.5μA;

(2)IO端口电容:≤1pF;

(3)IO端口击穿电压:≥6V。

2 电路功能设计

IO端口D+、D-是高速通讯端口,在抗静电设计时必须考虑既能满足抗静电要求,又不能影响数据传输速度,一个单独的TVS管无法做到既兼顾低的击穿电压又满足1pF左右的低结电容,所以采用TVS二极管T1与小的结电容二极管D1和D2串并联的方式来实现。我们称之为低电容TVS结构,如图2所示。

图2 低电容TVS 结构图

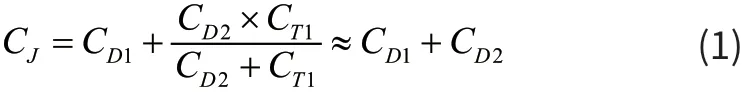

整个结构的总电容CJ就等于D2和T1的串联电容,再与D1的并联。计算公式如下:

由于电容CD2和CD1都很小,CT1要比两者大一个数量级,所以总电容CJ由D1,D2决定,约等于D1和D2结电容之和。

在图1中,两个IO端口采用相同的结构设计,但是共用一个TVS二极管,整个结构形成了端口对端口,端口对地的正反向静电泄放通道,以实现对端口的抗静电保护。

实际上我们可以扩展出更多的IO保护端口,以适应不同电路的需求,比如图3所示的具有8个IO保护端口的抗静电保护电路。

图3 8端口的抗静电保护电路

3 参数指标设计

■3.1 IO端口电容

在图2中,IO端口电容实际上是等效电容,主要由TVS管T1和低电容二极管D2、D1的结电容决定,见图2。

T1结电容分为两部分,势垒电容和扩散电容,当PN结加反向电压时,扩散电容可以忽略不计,结电容主要由势垒电容CB决定。计算公式如式(2)所示,其中A为PN结结面积,Na是P区的掺杂浓度,Nd是N区的掺杂浓度,Vbi是PN结自建电场,VR是外加反偏电压。

P+注入浓度为(1~4)E17/cm3,N区注入浓度为(1~4)E17/cm3,N型埋层的浓度为0.9E15/cm3,同时结合版图中PN结的面积A=0.158436mm2,计算结果:CT1=CB=2.79pF。

IO端口电容实际上取决于TVS管T1与二极管D2的串联,然后与二极管D1的并联,见图3。CD2的设计值为0.2pF,CD1的设计值为0.5pF。根据前文公式(1)计算出总电容。计算结果:CJ=0.92pF。

■3.2 IO端口击穿电压

该参数指标VBR在图2中应为T1管的击穿电压加上D2的正向导通压降,其中 T1击穿电压设计值为8.4V,D2正向导通压降约0.8V。

T1管的击穿电压我们按照单边突变结理论进行分析设计,有如下公式:

其中Ecrit为硅的临界电场(即:5E4V/cm),εs为硅的相对介电常数11.9,最后得出NB为0.9E15/cm3。由于TVS器件主要发生在N型埋层与P衬底之间,因此NB即为N型埋层的浓度。由于器件在研制过程中,N型埋层为首次光罩注入,后续工艺加工过程中有多次高温长时间的退火工序处理,会对埋层产生向上的反扩散,因此,在选择砷埋层注入时,须对埋层的反扩散做预估处理,即增加剂量以提高多次高温长时间的退火所带来的浓度下降。

■3.3 IO端口漏电流

在原理图2中,IO端口漏电流即为对地二极管D1的PN结在电压反偏置,同时没有达到击穿电压时通过二极管的微弱电流。当PN结加反向电压时,外电场使空间电荷区变宽,加强了内电场,阻止了扩散运动的进行,而加剧了漂移运动的进行,形成反向电流。

理想的PN结反向漏电流中包含了扩散电流与空间电荷区产生的电流两部分构成,而在硅器件PN结的耗尽层之间基本已经进入一个扩散的动态平衡或者叫做载流子耗尽状态,因此反向扩散电流已不起主要作用,而空间电荷区电流则起着主要的支配作用。因此我们主要对该空间电荷区电流进行分析计算。

PN结正常处于平衡状态时,势垒区内通过复合中心的载流子产生率大于复合率。当PN结处于反向偏置时,势垒区的电场加强,因此在势垒区通过复合中心所产生的电子空穴对来不及复合即被外界电场驱走,因此势垒区内通过复合中心的载流子产生率大于复合率,从而形成空间电荷区产生电流。该电流公式表述为:IG=qGXDA,其中,A为PN结结面积(图3中T1的PN结结面积),XD为势垒宽度,G为净产生率(即单位时间单位体积内势垒区所产生的载流子数)。由于在势垒区ni>>n,ni>>p,因此势垒区电流的净产生率G=ni/(2τ),代入上式即得出空间电荷区产生电流的计算公式:

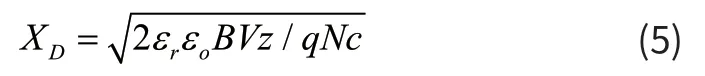

公式中ni为本征载流子浓度,XD为势垒区宽度,即为耗尽层宽度,由器件施加的反向电压所决定(取3.3V),计算公式如下:

因此代入所有数据,可以得出空间电荷区产生电流IG=0.055μA左右。该数据为理论计算结果,实际的漏电流会因为加工过程中的生产缺陷而有所增加,参考设计仿真部分的IO端口漏电流仿真结果,能够满足设计要求。空间电荷区产生电流即反向漏电流的大小还与构成PN结的半导体材料禁带宽度呈指数关系,同时该漏电流中还包含了表面漏电,而该表面漏电主要对工艺加工过程中生产缺陷(包括离子注入带来的晶格位错、介质淀积过程中引入的可动电荷等)的产生进行严格的控制。

4 设计仿真

■4.1 原理仿真

根据图2中的原理图,结合具体指标要求,我们把电路中各个元件的参数设置如下:T1击穿电压为8.2V,结电容为3pF; D1正向导通电压为0.8V,低电容二极管D2结电容为0.3pF,D1结电容为0.5pF。

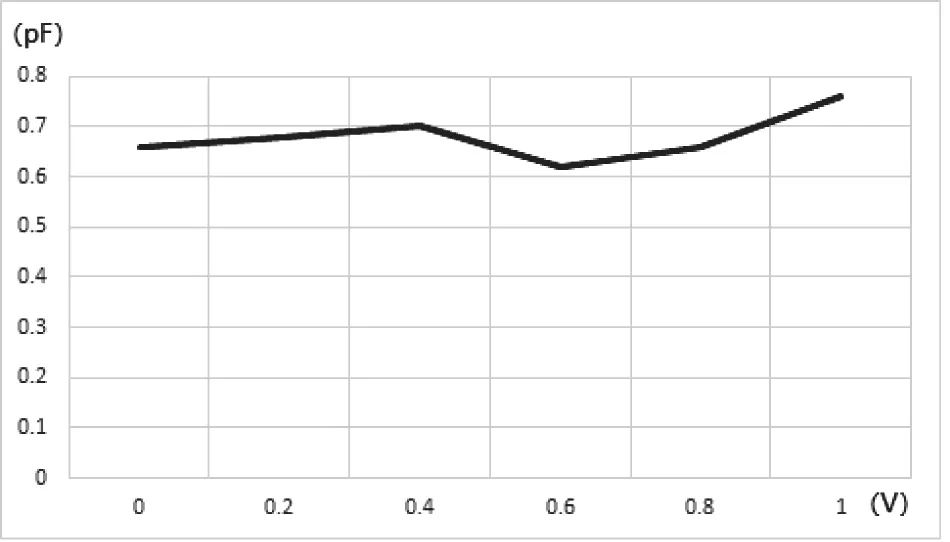

采用上述数据,对图2中的电路进行I/O端口SPICE仿真,仿真结果如图4和图5所示。结果数据如下:

图4 I/O端口的伏安特性曲线

图5 I/O端口电容特性曲线

(1)I/O端口击穿电压VBR=8.8V(I/O端口电流IIO=1.0mA);

(2)I/O动态导通电阻RDYN=0.82Ω(IIO=1.0A);

(3)I/O动态导通电阻RDYN=1.0Ω(IIO=1.5A);

(4)I/O端口总电容:CIO=0.62pF~0.76pF(CD2=0.2±10%,CD1=0.5±10%)。

经过SPICE原理仿真,验证了我们电路设计时各个二极管在参数分配上的可行性。

■4.2 版图设计

在完成原理仿真之后,进行了电路的版图设计,完成之后的版图如图6所示,管芯总面积为:718μm×392μm(不包含缓冲区和划片槽),图6中其实提供了四路IO保护端口,其中两路为备用,是为了防止在实际工艺加工过程中,可能出现的工艺不稳定,导致某一路的参数指标稍微大于设计值,可以用备用的两路当中的一路来代替。

在图6中,正中间的PAD下面是T1管,这个PAD只做晶圆测试用,实际封装时不使用。四个角的四个PAD下面是D1管,而旁边叉指状的为D2管。之所以设计成叉指状,是为了增大结面积,提高泄放电流的能力,而又不会明显增加结电容。

图6 抗静电保护电路版图

■4.3 工艺仿真

图7是低电容TVS结构一个通道的剖面图,对应图2中的原理图,二极管D1是由N-外延层、P+衬底和P型隔离形成的PN结构成。二极管D2是由P+注入和N-外延层形成的PN结构成,T1是由N++埋层和P+衬底之间的PN结构成。

仅仅对电路进行SPICE仿真是远远不够的,接下来我们采用TCAD软件对图7中的结构对进行实际工艺制作流程仿真,主要采用掺硼衬底中进行砷埋层注入后生长外延层。多通道(即I/O端口)对GND之间的TVS即依靠砷埋层与衬底之间的齐纳二极管实现,仿真代码如下:

图7 低电容TVS结构纵向剖面示意图

即衬底浓度取1E18/cm3,砷埋注入选择剂量7E15cm-2,能量100Kev。仿真击穿电压和击穿之前的漏电流如图8和图9所示。

图8 低电容TVS器件IO端口击穿电压仿真图

放大图8,根据仿真结果,I/O端口实际击穿电压为9.57V,满足设计要求。在IO端口击穿之前,IO端口的漏电流为pA级别(数值非常小,即几乎无漏电),IO端口漏流满足设计要求,具体如图9所示。

图9 IO端口击穿曲线击穿点局部放大

5 设计总结

■5.1 版图设计要求

为了满足电路设计,版图设计时应注意以下事项:

(1)所有层次尽可能地不能出现垂直拐角,而应保持一定的弧度,以保证良好的击穿特性;

(2)埋层与隔离之间的间距应保持足够的距离;

(3)为后续划片,版图中的芯片边界须做PAD刻蚀处理。

■5.2 工艺要求

为了满足电路设计,工艺设计时参考以下数据:

(1)晶圆衬底参数选取0.014Ω·cm~0.02Ω·cm;

(2)NBL埋层的浓度应该为:1E15cm-3;

(3)N-型外延参数为:30Ω·cm,厚度为10μm。

■5.3 关键工艺难点

在整个设计中,主要的工艺难点为:埋层注入后,在后续加工过程中多次的高温长时间退火工序,会给埋层浓度带来降低的风险,因此初始注入剂量应适当加量,并逐步试验出合适的剂量。

TVS器件主要为体击穿才能保证良好的电流能力,因此真正的击穿点应该为N型埋层与衬底之间的纵向方向,但是在实际过程中,往往由于埋层注入后随着高温长时间的多次工序介入,会带来埋层的横向扩散非常严重,如果最终埋层与隔离之间的间距小于实际击穿所需的耗尽层宽度,该TVS器件则首先发生在横向部分,大大降低过电流能力。因此在版图处理时,需要保证N型埋层与PBL+PISO之间的间距足够大。

6 结束语

完成电路设计和版图设计之后,经过仿真验证,技术指标满足设计要求。

由于电路的IO端口电容比较小,1pF以下,为了减小封装硅铝丝引线带入的寄生电容,在最终电路产品封装时,建议采用无引线小管壳封装,比如DFN或者SON的封装形式。我们为了降低成本最终采用了SOT-23塑料封装,见图10。

图10 电路封装尺寸