孙远航,李彧,倪晓波,孙增振

(网络通信与安全紫金山实验室,江苏南京,211100)

0 引言

随着芯片的集成度的提高,其接口种类越来越多功能也变得越来越强大。不同功能模块可以工作在不同的时钟域下,这就对传统的同步设计以及验证方法提出了挑战。特别是现在工艺制程越来越先进、手机等SoC 芯片时钟越来越快越来越复杂,这类问题愈显突出。如果这些跨时钟的地方处理得不当,那幺对于整个芯片来说可能是灾难性的。而随着近年来芯片研发的成本越来越大,其所造成的经济损失也是可观的。所以这就使得在芯片设计时必须很谨慎地去分析与对待异步信号跨时钟域的问题,在设计时就将问题考虑充分,避免这类问题影响芯片整体的功能及可靠性。

1 亚稳态与同步器

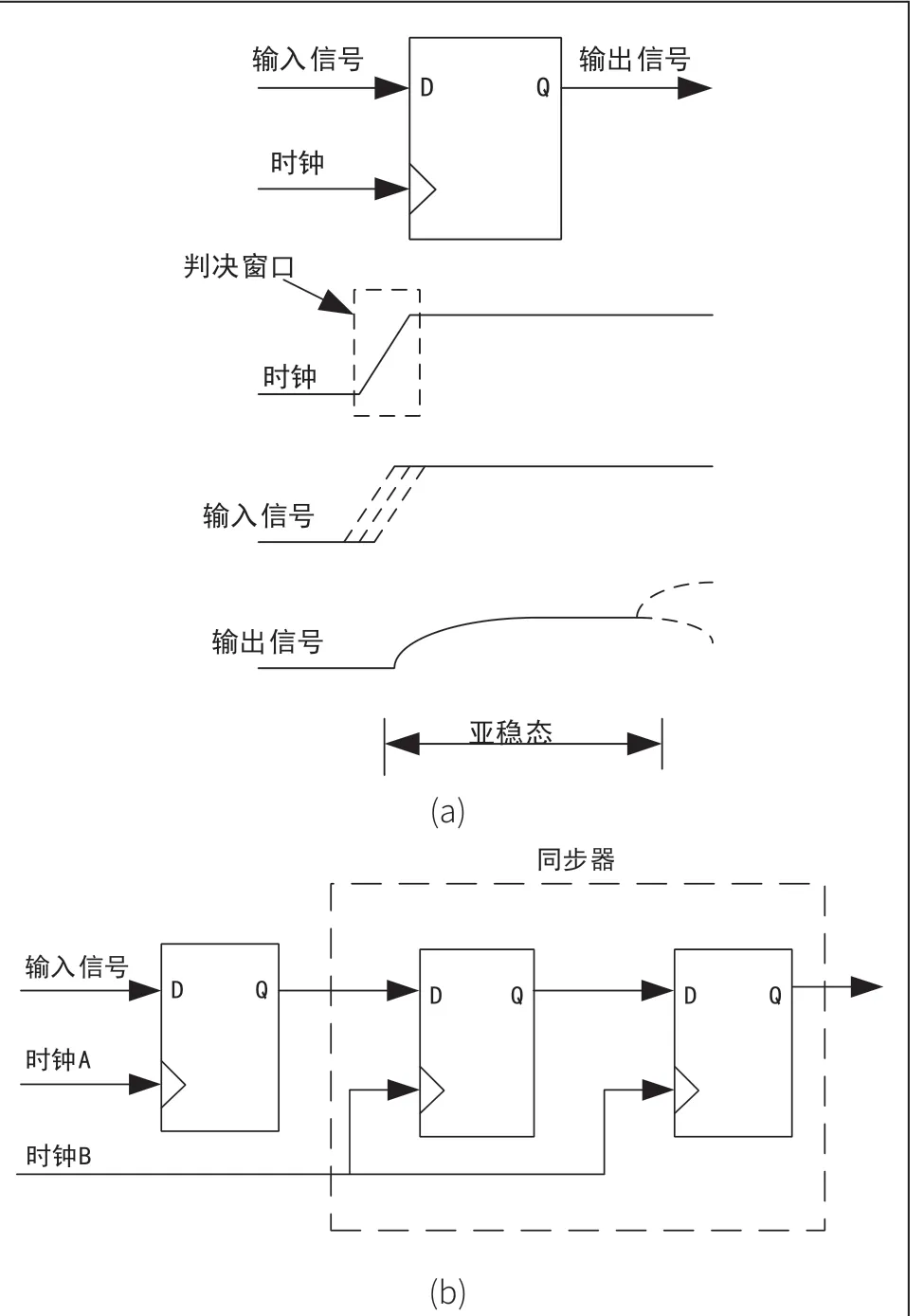

亚稳态指的是触发器无法在一个规定的时间达到一个确定的状态,当触发器进入亚稳态,我们既无法预测其输出的电平,也无法预测其何时才能稳定地输出正确的电平[1]。在亚稳态期间,触发器输出一些中间级电平,并且这种电平可以延通路传播,如图1(a)所示,其产生的原因是由于信号在时钟触发沿的判决窗口没有保持稳定,导致触发器中锁存信号的电容充电不足,从而使得触发器需要花很长的时间才能使输出信号达到标准电平,使电路“反应”变迟钝。亚稳态对我们的逻辑电路产生的危害包括:使输入的数据采样错误导致功能错误;扩散可能会导致后续的逻辑功能出错;扩散的亚稳态会导致所有扇出的器件进入振荡状态从而导致器件功耗增加,严重的可能会损坏器件等。

图1 亚稳态及同步器示意图

一个异步信号跨时钟域时,亚稳态是不可能从根本上消除的。我们在设计时所要做的是最大限度地减少亚稳态对电路的影响。通常我们用故障间隔平均时间(MTBF,mean time between failures)来衡量亚稳态对数字系统的影响,MTBF 越大则说明系统越安全[2,3]。其公式如下所示:

上式中c1 和c2 是常数,由器件的工艺与实际应用环境决定;fclk对异步信号进行采样的时钟频率;fdata是输入异步信号的反转频率;tMET是保证亚稳态不传输到下一级寄存器所允许的亚稳态持续最大时间。通过分析这些变量可以得出提高 MTBF 可以从以下方面入手:a.减小fdata即减小输入数据的翻转率;b.减小fclk即减小采样时钟的频率;c.增大tMET即增大从亚稳态到确定电平之间的判决时间;d.改良工艺参数c1 和c2 对MTBF的不良影响。

以上4 项改善 MTBF 的手段中,前3 项是我们作为数字设计工程师可以通过合理的设计来实现的。其中fdata及fclk主要由设计需求决定,工程师干预程度偏低,我们可以重点从增大tMET入手。从下面的公式和图2 可以看出,tMET主要与5 个因素有关,分别是时钟周期 T、时钟到输出延时tco(clock to output)、两寄存器之间组合逻辑延时与走线延时之和tdata,寄存器建立时间tsu以及两触发器之间的时滞tskew(tskew=tclk2-tclk1)。这5 个参数中T 由系统性能设计指标决定,tco和tsu由器件自身决定,tskew可以忽略不计,所以只有tdata是我们在设计是可以影响的。同步器是处理 CDC问题时所采用的主要器件,其通常由两个级联的触发器组成,如图1(b) 所示。当我们使用同步器对异步信号进行采样时,由于同步器两级寄存器靠得很近,tdata就变得非常小从而提高了tMET参数。

图2 各时钟参数示意图

下面介绍同步器具体改善MTBF 的例子。以一个0.25μm 工艺的 ASIC 库中的触发器为例,tMET=2.3ns,c2=0.31ns,c1=9.6as(las=10-18s),fclk=100MHz,fdata=1MHz,则根据之前的 MTBF 公式可以算出其故障间隔平均时间大约为20 天。如果将两个这种触发器串联作为同步器使用,则这个同步器的 MTBF 可以由以下的公式算出,大约是9.57×1010 年,而宇宙年龄大约是1010 年。

从上面介绍可以看出,采用多级寄存器级联结构的同步器对提高系统的 MTBF 有很大的帮助,所以在项目中,凡是需要跨时钟的地方一定要使用后端厂商提供的同步器来处理,如果后端厂商没提供专门的同步器单元,那幺需要前端设计师在代码中对需要同步的信号做打拍处理(至少两拍)并且要求后端工程师在后端设计中保证几级同步器寄存器靠得足够近。

2 常用的CDC 处理方法

本节主要介绍4 种常用的CDC 处理方法,分别是信号同步器、多周期路径MCP(Multi-Cycle Path)同步法、握手协议以及异步FIFO。

■2.1 信号同步器

信号同步器的结构是四种方法中最简单的,它是由同步器直接演化而来,根据功能的不同又可以分为电平信号同步器、边缘检测信号同步器以及脉冲信号同步器。

电平信号同步器如图1(b)所示,它仅由一个同步器构成。其输入信号的电平宽度至少应该是同步时钟周期的两倍,否则可能由于亚稳态导致电平信号在跨时钟域时丢失如图3 所示[4]。

边缘检测同步器结构如图4 所示,它在电平信号同步器之后又加了一级寄存器和一个与门。这一电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。将与门改为与非门可以构建一个产生低电平有效脉冲的电路。

图4 边缘检测信号同步器

当输入脉冲信号的宽度大于同步时钟周期与第一个同步触发器所需保持时间之和时,我们仍然可以使用边缘检测信号同步器来同步脉冲信号,但是当快时钟域单时钟脉冲进入慢时钟时,边缘检测信号同步器就无法在正常工作了,需要采用脉冲信号同步器来实现相应的功能,如图5 所示,每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。

图5 脉冲信号同步器

■2.2 多周期路径同步法

上面介绍的3 种信号同步器是同步单 bit 信号时所常采用的方法,当需要同步的信号是 bus 型的数据时再采用上面的方法就不适合了,因为bus 型的数据每一bit 经过同步器之后可能由于亚稳态的情况而出现bit 之间传输延时不一致的情况。多周期路径同步法提供了一种简洁的处理多 bit信号跨越时钟域的解决方法,其电路如图6 所示。

图6 多周期路径同步法

从图中可以看出多周期路径同步法其实是由脉冲信号同步器演化而来,其中控制通路就是一个脉冲同步器,当输入拥有数据常要跨时钟时,数据通路先将数据进行锁存,控制路径将数据有效使能脉冲同步到接收侧,并用还原出的脉冲信号做选择器的使能对数据总线上的数据进行采样。这种同步多 bit 数据的方法结构简单而且比较安全,由于控制通路使用脉冲同步器,在发送侧就不需要根据不同时钟频率来推算数据有效使能需要保持多少时钟周期,并且由于只对有效使能单bit 进行跨时钟处理,而数据路径在采样时至少已经在数据路径上保持了3 个时钟周期,这就保证了(在后端时序约束时还是需要对数据路径的到达时间进行约束)数据不会在接收时钟采样沿处发生跳变,从而避免了数据路径亚稳态的发生。但由于这种同步机制是一种开环的同步机制,在收发两侧没有交互机制,所以发送侧何时可以安全的更新数据无法得到保障,这些问题由接下来的新机制加以解决。

■2.3 握手协议

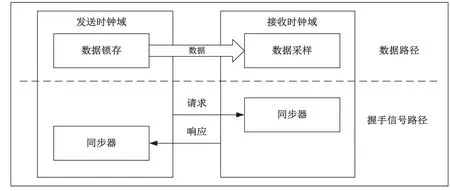

上面提到的多周期路径同步法是一种有效的数据 CDC 方法,但是也提到由于是开环路径无法做到收发两侧信息交互,握手协议可以很好的解决这一问题。握手协议是一种闭环的数据同步方法,其主要结构如图7 所示。它主要分为两大路径,分别是握手信号路径和数据路径。握手信号指示接收时钟域的何时可以对总线数据进行采样,以及源电路何时可以更新当前数据锁存器中保存的内容。数据路径主要由发送时钟域的数据锁存模块以及接收时钟域的数据采样模块组成。当有数据需要传输时发出请求信号,并将数据锁存在数据锁存器中。当请求信号在接收时钟域被同步后,以此为依据将总线上的数据进行采样,并向发送时钟域发送响应信号[5,6]。

图7 握手协议主要跨时钟路径

图8 是一个典型的握手协议电路结构图。从图中可以看出,它与图6 最大的区别是增加了一条由接收侧向发送侧反馈的控制路径。当输入数据有效时,输入数据被锁存数据跨时钟进程开始,数据有效信号由绿色路径向接收侧传输,在接收侧对其进行同步之后并将恢复出的脉冲信号为使能对蓝色数据总线上的数据进行采样。采样结束后接收侧将反馈信号沿紫色路径反馈,发送侧接收到这一反馈信号后表明当前数据已经被对端安全采样,可以自行决定是否对数据通路进行刷新传输新的数据。

图8 握手协议基本电路结构

■2.4 异步 FIFO

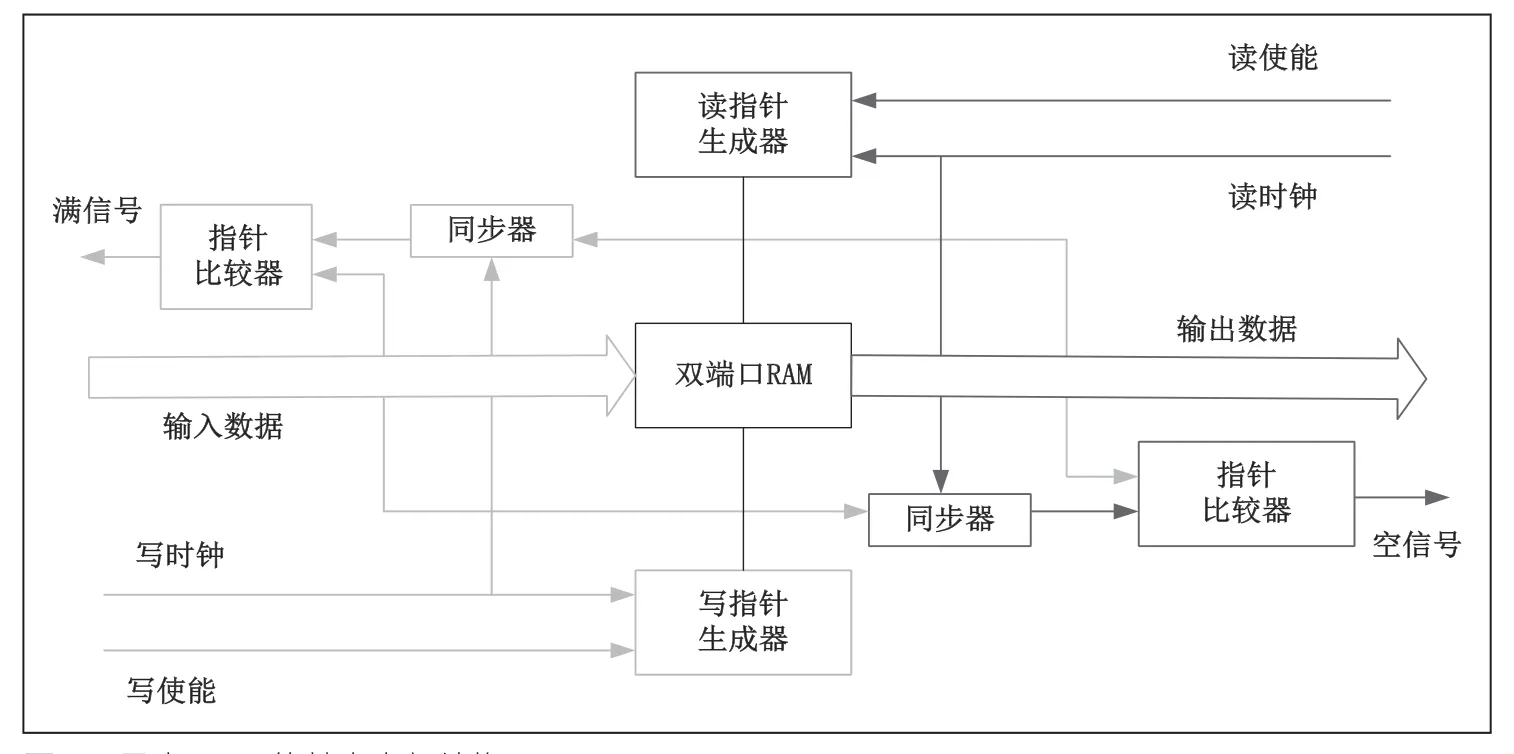

在许多设计中,有些需要跨时钟的数据是burst 发送的,或者两个时钟域之间的数据需要做速率匹配,这时握手协议就很难来实现了,这时就需要引入异步FIFO。图9 所示的是异步FIFO 的基本内部结构,蓝色部分是写时钟域,紫色部分是读时钟域。其内部主要由读写指针生成器、读写指针比较器、同步器以及双端口RAM 组成。读写指针生成器主要根据读写便能对读写指针进行累加,并将累加之后的指针进行格雷码变换,由于格雷码相邻码元之间只有1bit 发生反转的特点,在读写指针进行跨时钟同步的过程中可以有效地控制亚稳态导致的读写指针传输的误差范围;读写指针比较器是将同步之后的读写指针再进行逆格雷码转换,与本地当时刻产生的读写指针进行对比,并根据对比的结果输出空满信号,对上下级逻进进行反压处理;跨时钟的数据则通过双端口RAM 做跨时钟隔离[7]。

图9 异步FIFO 的基本内部结构

以上介绍的4 种信号跨时钟域的方法在我们的设计中都有使用,具体使用哪一种方法需要对应具体情况进行分析,在对于跨时钟信号是单bit 信号的时候推荐使用信号同步器来实现;在对应跨时钟信号是总线仲裁类或者缓变化bus型数据时推荐使用多周期路径同步法或者握手协议来实现;当需要跨时钟的是主数据路径时,例如一些接口协议需要做速率四配时,推荐使用异步FIFO 来处理[8,9]。

3 结束语

本文主要介绍了 RTL 设计中的 CDC 问题,分析了亚稳态产生的原因以及解决的方法。重点介绍了在设计中常用的4 种信号跨时钟的处理方法,并分析了一些设计中处理异步信号时常见的错误并给出了相应的改进意见。CDC 问题在设计中虽然不起眼,但是业界中很多失败的案例都是由它引起的,特别是现在先进设计中可能会用到先进工艺、逻辑规模又异常大,从而导致成本非常高。同时也正是由于这些问题不起眼,在验证与时序分析阶段有时很难定位和发现这类问题,所以对于RTL 开发来说,作为芯片设计的最前端应该把这类问题消灭在源头,这对于时间和成本来说都是最划算的。