牟云飞,黄菊莲,王彩云,李燕

(西安西谷微电子有限责任公司,陕西西安,710000)

0 引言

随着FPGA/CPLD 的不断普及和制造工艺的不断更新,FPGA/CPLD 芯片的安全性和可靠性方面也提出了新的要求。很多专家学者在不断地研究FPGA/CPLD 的测试方法和技术[1]。作为第三方测试行业对FPGA/CPLD 测试业务也急剧上升,测试覆盖率和测试流程也要求符合生产可操作性,同时也要求更短的测试周期。因此对于基于ATE 的FPGA/CPLD 测试技术的研究显得尤为重要。

从制造设计的角度来讲,CPLD/FPGA 测试是指对FPGA 器件内部逻辑块和可编程互联线、输入输出块等资源的检测[2]。但是作为第三方检测行业的测试方案是通过软件配置被测CPLD/FPGA,ATE 测试时基于特定的配置逻辑施加测试激励并接收响应来判定逻辑功能。因此对被测器件测试流程和功能测试覆盖提出了更高的要求。

本文提出在线测试方法在筛选企业中主要有以下优点,第一,改善测试的操作模式,使测试操作更加简单快捷,简化操作,减轻生产操作流程;第二,可以对FPGA/CPLD 进行多次逻辑配置,提高测试覆盖率打下基础;第三,减少FPGA 测试时使用的硬件配置PROM,从而降低由于外围电路的引入造成的测试风险。

在线测试通过配置完成后,可以在J750HD 对芯片进行直流参数和功能测试。

1 硬件结构

测试系统结构如图1 所示,主要由四部分组成,自动化测试设备ATE 是控制的主体,实现全部的功能测试、参数设置判断、数据存储与显示;测试开发板是测试的主体,通过连接器与ATE 硬件资源接通。接收ATE 发来的控制信号,返回测试结果与测试数据;DUT 测试芯片通过适配器与开测试开发板接触;硬件结构和适配器主要连接接口部分。

图1 硬件结构示意图

图2 在线测试方案流程图

2 在线测试方案流程

在线测试方案流程图分三个阶段:

第一阶段:方案确定及设计阶段,包括方案确定、原理图设计、测试专用板设计、PCВ 设计。

第二阶段:测试程序编写与测试向量生成阶段。包括边界扫描测试、被测器件内部资源逻辑设计、编写测试代码(根据不同厂家FPGA/CPLD 选择仿真编程软件Quartus IIISEDiamond 及波形仿真工具)综合布局生成svf 文件、解析svf 文件、编写脚本转换工具、测试向量生成。虚线框图内在技术实现重点介绍。

第三阶段:测试程序加载调试与最终测试数据回读。

3 技术实现

■3.1 Verilog 语言逻辑设计

CPLD/FPGA测试之前要对被测器件进行特定逻辑配置。原测试方法配置逻辑使用的原理图输入,缺点是效率低,查错困难且绘制原理图比较花费时间。该项目使用 Verilog 语言完成配置逻辑输入以及综合验证平台的搭建,并用仿真工具对所设计的逻辑功能进行验证。

■3.2 输入配置逻辑转换向量

(1)解析IEEE 1149.1 JTAG 协议。

(2)解析综合生成的.SVF 文件。

(3)用脚本语言(python/perl)编写脚本转换工具。

(4)解析边界扫描ВSD 文件,提取IDCODE 指令。

(5)将SVF 文件转换为相应ATE 测试设备能识别的测试向量。并验证逻辑功能。

(6)运用仿真软件(如Modelsim)工具进行逻辑功能的波形仿真验证功能逻辑。

(7)拆分转换测试向量,进行读ID 操作、擦除操作、查空操作、编程功能验证、校验操作。

■3.3 重复配置

FPGA/CPLD 内部的主要模块包括:可编程逻辑模块(CLВ)、可编程逻辑互连(IR)、输入输出模块(IOВ)、ВRAM 和乘法器。重复在线配置可以实现多次功能验证,提高测试覆盖率、故障率、完整性、降低测试风险。

■3.4 JTAG 接口通信协议解析

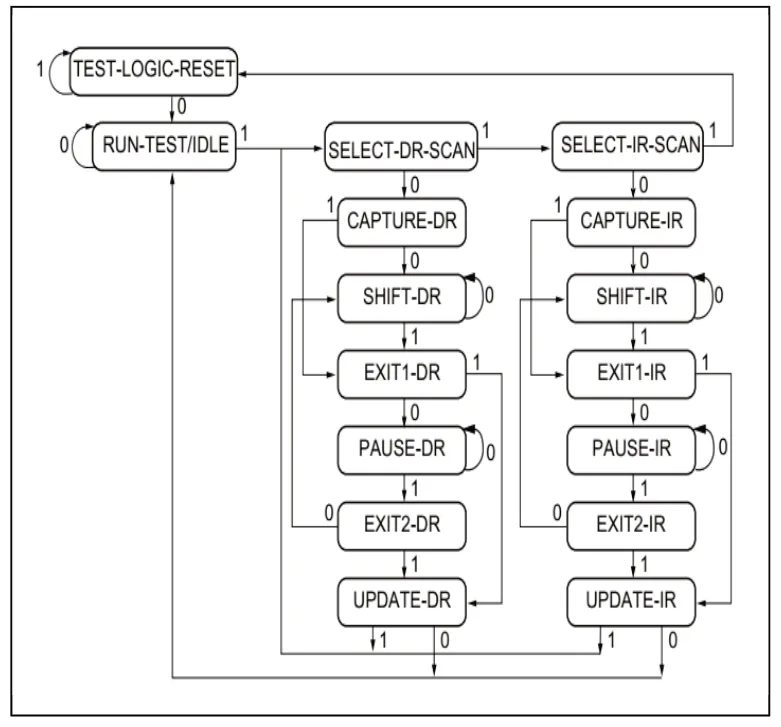

本技术最主要的理论依据为IEEE 1149.1 协议,也称为JTAG 协议,该协议由TMS、TCK、TDI、TDO 四个信号管脚16 个状态机实现信号传输,其中状态的跳变由TMS 决定。TDI/TDO 传输数据寄存器和指令寄存器的数据和指令。图3 为JTAG 协议状态机流程图。

图3 JTAG 状态机

■3.5 JTAG 接口通信协议解析

SVF 代码是转换成ATE 测试机台可执行文件的关键文件,它的组成部分主要有:初始化寄存器、读器件ID、编程、校验、擦 除、擦空。通过将SVF指令代码用脚本工具转化为测试设备识别的测试向量。那幺测试设备将对被测FPGA/CPLD 器件进行读器件ID、编程,校验,功能测试、擦除,擦空操作。并且可以将不同设计输入所生成的SVF 文件转换成测试向量进行第二次编程,校验,功能测试、擦除,擦空操作。此操作为了多次配置设计输入提高被测FPGA/CPLD 器件测试覆盖率。下面将详细解析svf 文件。

Svf 中各个指令与IEEE1149.1 的状态机的对应关系如表1。

表1 JTAG状态机与指令集对应关系

Svf 指令解释:

(1)ENDDR,ENDIR:设置DR/IR 扫描操作后,JTAG应移到稳态;

(2)FREQUENCY:设置JTAG 时钟的工作频率;

(3)HDR,HIR,TDR,TIR:设定自动添加于DR/IR数据前(H)、后(T)的比特序列;

(4)PIO:设定系统管脚的输入输出数据;

(5)RUNTEST:描述状态机在设定的周期或时间内,移入某个稳态并保持的操作;

(6)SDR、SIR:描述移入/移出的目标寄存器(数据寄存器和指令寄存器);

(7)STATE:描述将状态机移入某个稳态的操作;

(8)TRST:描述TAP 的复位信号。

在线操作包括ID 操作、擦除操作、查空操作、编程功能验证、校验操作。

■3.6 脚本工具

根据svf 解析文件编写脚本,脚本实现将综合生成的svf 文件转换成测试设备所能识别的测试向量。目前该脚本实现ALTERA、XILINIX、LATTICE 三个厂家的FPGA/CPLD,转换格式可以覆盖两款测试设备,分别为日本ADVANTEST 厂家的自动化测试设备T6575 和美国TERADYNE 厂家的J750 设备。脚本主要分三个模块主要功能介绍如下。

图4 脚本框架图

图5 脚本转换界面

(1)接口模块svf_conv.pl:分解数据(TDI,TDO,MASK,SMASK)

①分解命令为状态的迁移

SCAN 指令:当前状态→SHIFT →EXIT1 →ENDIR/ENDDR

RUNTEST 指令:当前状态→RUNTEST 状态→结束状态

STATE 指令:当前状态→STATE 状态

②根据状态的迁移产生TMS 序列

③对于各过程产生TDI/TDO 序列

④封装各管脚数据并返回

(2)解析模块svfFile.pm

①分类处理SVF 命令 SSDR、SIR、RUNTEST、STATE

②解析状态迁移过程,生成对应的TMS 激励

③生成相应的TDI 输入激励及注释

④生成相应的TDO 输出期望值

(3)输出模块

负压降尘装置主要针对截割头截割处的粉尘进行捕捉处理。掘进条件为:采用ø700 mm截割头,截割速度为80 mm/min。

①获取解析产生的激励数据

②生成向量,压缩重复行各管脚取一位数据生成向量;缓存向量;生成下一条向量;比较与缓存内容是否相同;

③生成输出文件根据测算机台需求转换为ATP 文件和ASC 文件

脚本命令帮助信息窗口

--help :显示脚本支持的命令

--in:指定svf 文件或者文件夹

--T:测试向量格式为TERADYNE J750 设备,默认为该设备格式

--A:测试向量格式为ADVANTEST T6575 设备

--debug:打印提示信息

--version:打印版本信息

脚本工具转换测试向量界面的截图,转换脚本也提供了友好的操作界面,上述帮助指令有利于快速执行转换指令。

■3.7 方案完成实施

在线测试方案已完成altera 厂家CPLD/FPGA 的验证,XILINX 厂家的CPLD/FPGA 验证,LATTICE 厂家的FPGA(该厂家可编程逻辑器件均内部有flash 空间,所有统一称FPGA)的验证。三大厂家共验证30 多种,10000 多只器件。测试方案通用性强,测试稳定,高效。

表2 是ATE 在线测试方案与原有测试方案比对情况。

表2 在线测试方案与原有测试方案比对情况

4 后期研究方向

后期主要研究方向包括两方面,第一,重复配置逻辑覆盖到CPLD/FPGA 器件关键功能单元;第二,利用verilog语言编写testbench 测试激励,并且将测试激励通过脚本转换成测试向量,实现重复测试用例验证,提高测试覆盖率。