李金凤,黄纬然,赵雨童,郭巾男

(沈阳化工大学 信息工程学院,辽宁 沈阳 110142)

0 引 言

随着工业相机的迅速发展,图像的分辨率以及帧频不断提高,以至对图像存储系统的要求也越来越高。DDR3 SDRAM(Synchronous Dynamic Random Access Memory)具有容量大、功耗低、体积小等优点,成为目前数据缓存的主流。DDR3 采用时钟双沿工作,有效地提升了存储速率。设计高效的数据访存控制器,克服DDR3 操作复杂的弊端,提高访存速率至关重要[1]。异步FIFO 接口时序简单、操作便利,降低对DDR3 进行读写操作的控制复杂度,广泛应用于跨时钟域数据采集系统中[2⁃3]。为解决帧交错问题,文献[4]通过分区缓存和乒乓操作提高缓存速率。文献[5]采用预取访问长度的数据缓冲机制,提高访存效率。

本文以Kintex⁃7 FPGA 为控制核心,在MIG 7Series 4.0 IP 核的基础上,提出异步FIFO+RAM 的读写仲裁控制方法,提高DDR3 SDRAM 的访存效率。将数据以帧为单位进行不完全乒乓操作,实现8 路RGB888 视频图像数据的实时、完整显示,解决跨时钟域数据交互中存在的帧交错问题。

1 系统方案设计

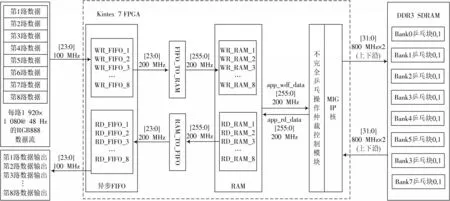

本文提出的DDR3 SDRAM 高速图像数据访存控制器结构如图1 所示。

图1 FPGA 读写数据缓存系统设计框图

系统包括FIFO、RAM、不完全兵乓操作仲裁控制模块、MIG IP 核及DDR3 芯片等。输入数据为8 路分辨率为1 920×1 080 的并行RGB888 格式(即图像的每个像素由24 bit 数据表示)图像数据。每一帧图像的数据量为:1 920×1 080×24 bit=47.46 Mbit。DDR3 SDRAM 选用Micron 公司的MT41J256M16⁃107 芯片。采用两片DDR3 芯片并联模式,即公用地址信号线、控制信号线、数据信号线。位宽为32 bit,总容量为256 M×32 bit=8 Gbit。用户接口位宽为256 bit。

DDR3 SDRAM 内部有8 个Bank,将8 路数据分别缓存在8 个Bank 中。图像数据的读取速度不低于采集速度,因此设计不完全乒乓操作保证帧完整性。将每个Bank 按地址平均分为两部分:乒乓块0 和乒乓块1,每个乒乓块存储一帧数据。设置8 个读、写FIFO 缓存8 路图像数据,每个FIFO 大小为24 bit×1 920,缓存一行图像数据。设置8 个读、写RAM,每个RAM 大小为256 bit×192。256 bit 数据的低240 bit 存放10 个像素图像数据,高16 bit 为标识位,标识数据来源。WR_FIFO 顺序读取一路图像数据,读完一行图像数据后将其缓存进对应的WR_RAM 中。仲裁控制模块将WR_RAM 缓存至DDR3对应Bank 的乒乓块。数据输出模块一直读取RD_FIFO中存储的数据。

仲裁控制模块根据反馈信号控制RD_FIFO 从RD_RAM 中 读 取 数 据;RD_RAM 从DDR3 的Bank 乒 乓块中读取数据。

1.1 MIG IP 核接口配置

根据Xilinx 公司提供的MIG IP 核,按硬件合理配置MIG IP 核。系统采用易于操作的UI(User Interface)接口模块建立FPGA 内部控制逻辑与外部存储器之间的访问连接[6⁃7]。

MIG IP 核包括用户接口、存储器控制器及物理层三部分。用户接口位于MIG IP 核最前端,控制DDR3 进行读、写操作。存储控制器位于用户接口和物理层之间,提供两模块间的数据传输及处理物理层的接口请求。物理层后端连接外部存储设备,负责产生DDR3 所需要的信号时序并捕获DDR3 发出的数据。当app_rdy及app_en 信号为高,地址信号app_addr 与命令信号app_cmd 有效,用户逻辑连续发送有效读命令;经过若干个周期等app_rd_data_valid 信号为高时,读出数据app_rd_data 有效。app_rdy 及app_en 信号为高时,地址信号app_addr 与命令信号app_cmd 有效,当app_wdf_rdy及app_wdf_wren 信号为高时,写入数据app_wdf_data有效。

1.2 异步FIFO 模块设计

信号跨时钟域容易产生亚稳态[8⁃9]。异步FIFO 可解决跨时钟域问题,其结构如图2 所示。VIVADO FIFO IP 核支持的读写位宽比仅为1∶8,1∶4,1∶2,1∶1,2∶1,4∶1,8∶1。系统采用FIFO+RAM 的缓存方式,将图像数据写入FIFO 后再经RAM 缓存到DDR3,使得设计的FIFO 读写位宽比为10∶1。

图2 跨时钟域异步FIFO

2 读写仲裁控制方法

2.1 不完全乒乓操作设计

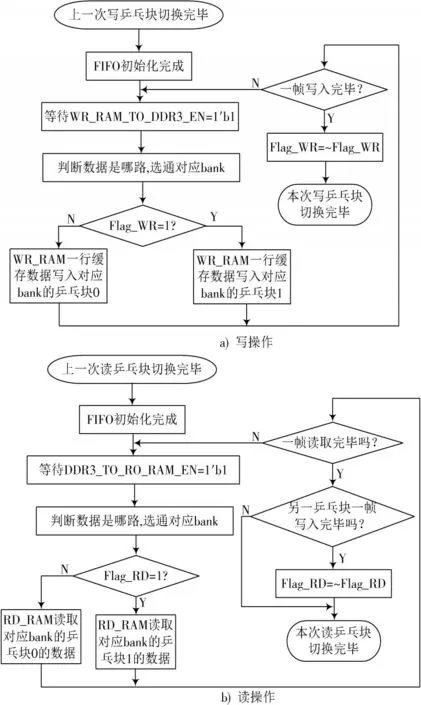

为解决对整帧图像数据进行连续读写操作存在的前后帧交错问题,本文提出不完全乒乓操作方法,如图3 所示。

图3 不完全乒乓操作读写流程

由于图像数据的读取速度高于采集速度,设置写操作的优先级高于读操作[10⁃11]。Flag_WR、Flag_RD 为乒乓块切换标记。写操作时,一帧数据(1 080 行)写入完毕后,切换到该Bank 的另一乒乓块写入下一帧数据。读操作时,一帧数据读取完毕后,判断另一乒乓块的下一帧数据是否完成写操作。若写操作完成,则改变Flag_RD 标记,切换到该Bank 另一乒乓块读取下一帧数据,否则继续读取当前乒乓块数据。

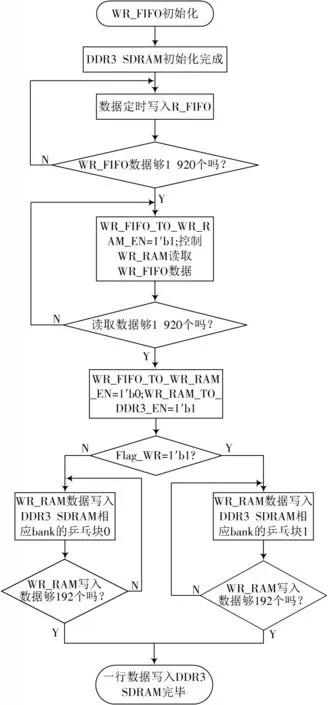

2.2 数据读、写控制方法

当外部视频图像数据采集完成时,将数据逐行缓存至WR_FIFO[12]。当WR_FIFO 的数据深度大于1 920 即一行数据存储完成时,控制模块将WR_FIFO 中的数据进行转换后缓存至WR_RAM,WR_RAM 请求DDR3 写入数 据。Flag_WR 为1 时,DDR3 将WR_RAM 数 据写入相 应Bank 的 乒 乓 块1;Flag_WR 为0 时,DDR3 将WR_RAM 数据写入相应Bank 的乒乓块0,流程图如图4所示。

图4 图像数据写入DDR3 流程

当DDR3 初始化或读写地址重新加载时,WR_FIFO及RD_FIFO 进行复位,清除数据[13]。RD_FIFO 数据小于1 920 个时,RD_RAM 请求读出DDR3 缓存的一行图像数据(192×256 bit)。若Flag_RD 为1,则从相应Bank的乒乓块0 中读取数据;若Flag_RD 为0,则从相应Bank的乒乓块1 中读取数据。R_RAM 数据读取完成后,将数据转换后写入R_FIFO 中。

3 系统测试结果

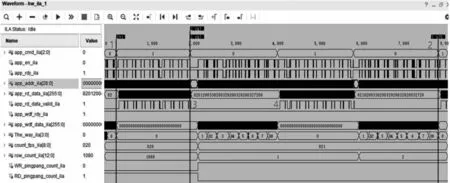

本文在Kintex⁃7 XC7K325TFFG676⁃2 的FPGA 芯片上测试系统。片外并联2 片MT41J256M16⁃107 DDR3芯片。8 路分辨率为1 920×1 080 的RGB888 视频图像并行输入,帧率为48 Hz。通过VIVADO 软件的ILA 抓取波形,结果如图5 所示。ILA 采样时钟为200 MHz,视频数据读取时钟频率100 MHz。The_way_ila 信号标识数据来源(第1,2,…,8 路);app_rd_data_ila=1 表示读数据有效;app_cmd_ila 为3’b001 时表示读使能,为3’b000 表示写使能。The_way_ila 表示将采集得到的1~8 路视频数据缓存至DDR3 SDRAM。

由标号1,2 知在周期291~7 975 时间内,一共对8 路数据完成了2 次写、读操作,时间开销为:7 975-291=7 684 时钟周期。周期内读写数据1 920×4(写2 行、读2 行)×8(8 路数据)×24 bit,可以计算有效带宽利用率为:

(1 920×4×8×24 bit)÷(7 684×256 bit)×100%=74.96%

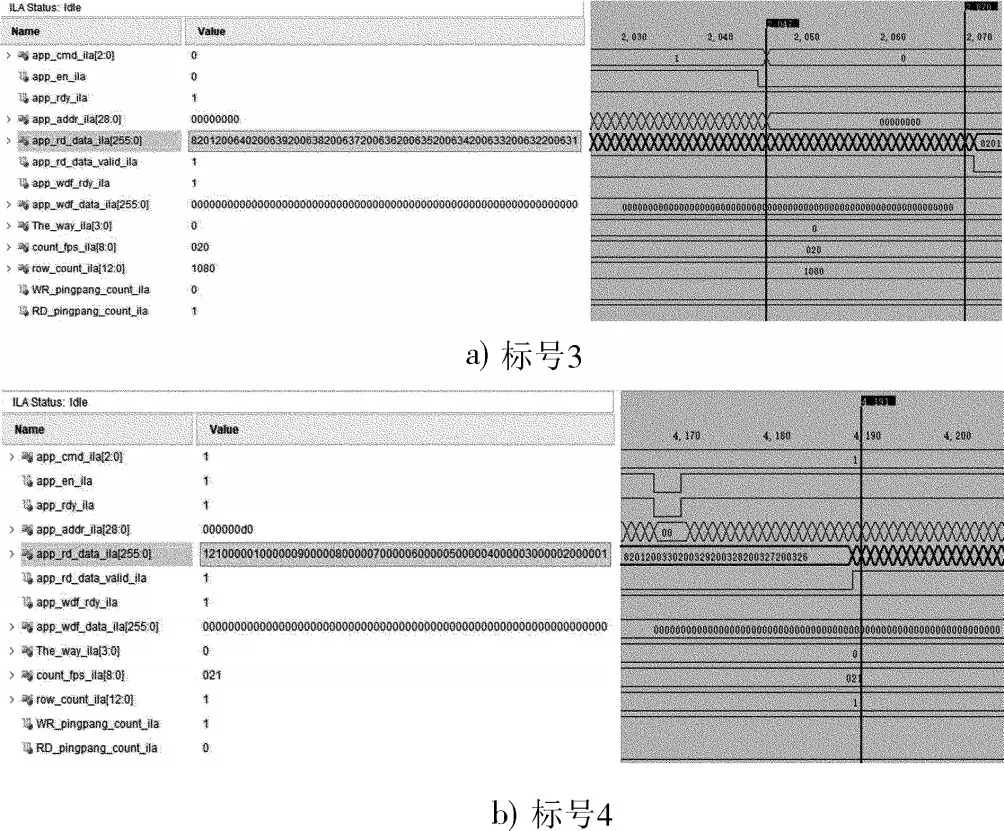

将图5 的标号3,4 进行局部放大得到图6。图6a)对应图5 中标号3 的放大图,图6b)对应图5 中标号4 的放大图。由图6a)可知在2 047 周期,app_en_ila 信号为高,地址信号app_addr_ila 与命令信号app_cmd_ila 有效。app_cmd_ila 为“001”表示读使能;count_fps_ila 为“020”表示正在读取第20 帧;row_count_ila 为“1 080”,表示正在读取第1 080 行,即向DDR3 发出读出第8 路输入第20 帧第1 080 行最后一个数据命令。经过23 个时钟周期延迟后,在2 070 周期数据输出。此时,app_rd_data_valid_ila 为1,表示读出数据有效;app_rd_data_ila 高16 位为“8 201”,其中“8”表示读取第8 路输入数据,“20”表示数据第20 帧,“1”表示乒乓块1,RD_pingpang_count_ila 一致;低240 位存储连续的10 个像素图像数据,结果正确。

图5 DDR3 SDRAM 读写缓存时序图

由图6b)可见在4 191 周期,row_count_ila 为“1”,表示正在读取第1 行,行切换正确;app_rd_data_valid_ila为1,表示读出数据有效;app_rd_data_ila 的高16 位为“1210”,表示第1 路输入数据的第21 帧,从乒乓块0 读出数据,与RD_pingpang_count_ila 一致,低240 位存储连续的10 个像素图像数据,即读取第21 帧第1 路输入的第1 行第1 个数据。乒乓操作运行正确,帧数据完整,克服了帧交错问题。

图6 DDR3 SDRAM 读写缓存时序部分放大

由波形图可知,本系统在48 帧频下8 路数据正常存储,在实际应用30 帧频下数据更加稳定可靠,有较强可移植性。由测试结果可知,本文设计的FIFO+RAM 缓存模块运行正确,不完全乒乓操作有效解决了高速视频图像在跨时钟域数据交互中存在的帧交错问题,提高了带宽利用率。

4 结 语

本文以Kintex⁃7 FPGA 为主控制器,结合Xilinx 提供的MIG 7 Series 4.0 IP 核,设计基于异步FIFO 的DDR3 SDRAM 高速访存控制器,实现8 路RGB888 格式并行视频图像数据缓存读、写控制,提出了不完全乒乓操作方法克服帧交错问题。经验证,8 路1 920×1 080@48 Hz 的图像数据帧完整,带宽利用率达到74.96%,满足高分辨率图像实时显示要求。灵活高效的DDR3 SDRAM 访存机制满足不同图像格式需求,具有较强的可移植性和实用价值。