单 伟 袁 航 钟思洁 郑 晓 赵梦薇

(中国核动力研究设计院核反应堆系统设计技术重点实验室,四川 成都610213)

0 引言

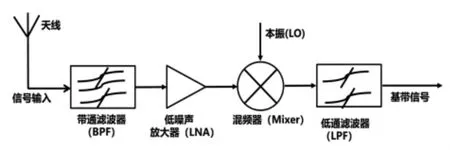

低噪声放大器(Low Noise Amplifier,LNA)被广泛用于雷达、航天测控、卫星通信等领域[1-3]。作为微波与毫米波通信系统前端接收机的第一级关键电路,LNA的增益、噪声系数以及线性度等性能将直接影响接收系统的指标性能[4]。典型的接收机前端链路如图1所示。在低噪声放大器的电路设计中,晶体管性能影响着带宽和最大增益。赝同晶高电子迁移率晶体管(Pseudomorphic High Electron Mobility Transistor,PHEMT)被广泛应于低噪声放大器的电路设计,因为其具有以下多重优势:工作频率高、噪声低、电流处理能力强、温度稳定性好、跨导大、输出电阻大等[5,6]。

图1 射频接收机前端链路框图

本文使用赝晶型高电子迁移率晶体管(PHEMT)设计了一款工作频段为32~38 GHz的低噪声放大器,通过三级级联电路结构实现低噪声放大器的高增益和最大传输功率。

1 有源器件和工作点的选择

本文设计的低噪声放大器的工作频段高,且要求的增益较高,噪声系数较低。综合考虑,最后选择了GaAsPHEMT器件的小信号模型进行仿真设计。

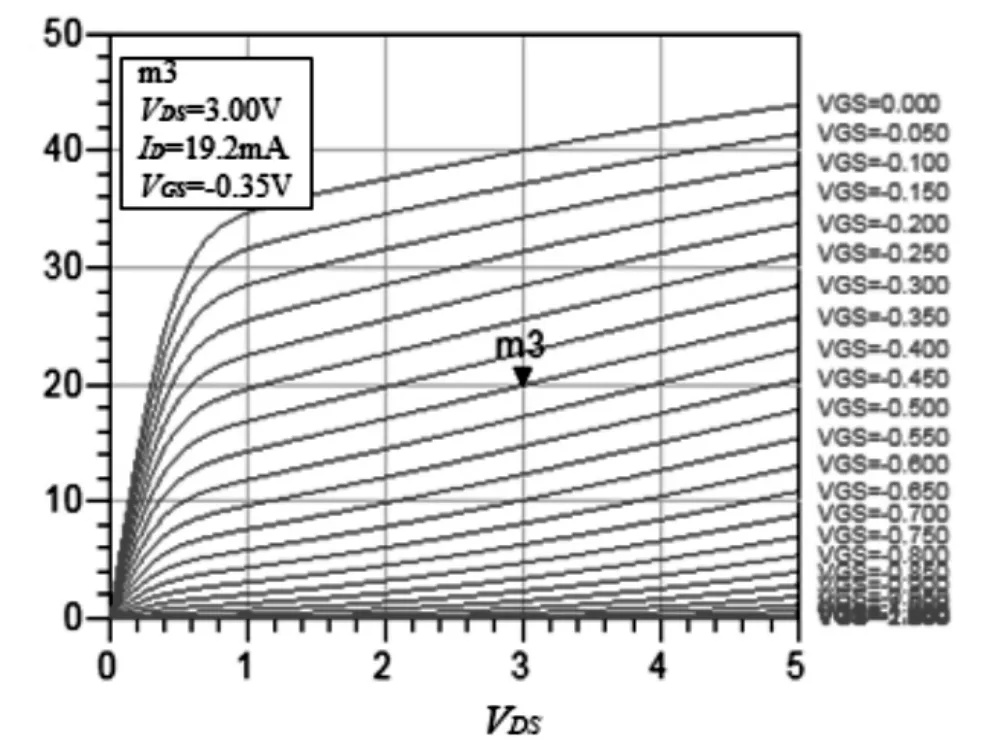

PHEMT器件的工作点选取直接影响着放大器的工作频段范围内噪声系数、带内增益以及放大器电路的稳定性[7]。通过计算机仿真软件对GaAs PHEMT器件在不同栅压下进行直流扫描仿真,对比漏极电流ID与漏压VDS的特性曲线如图2所示。结合图2的PHEMT器件转移特性曲线,在漏压VDS=3.0V,选取栅压VGS=-0.35 V,此时晶体管在最佳直流偏置点状态,相对应的漏极电流ID=19.2 mA。

图2 漏极电流I D与漏源电压V DS的特性曲线

2 电路设计

2.1 电路整体结构设计

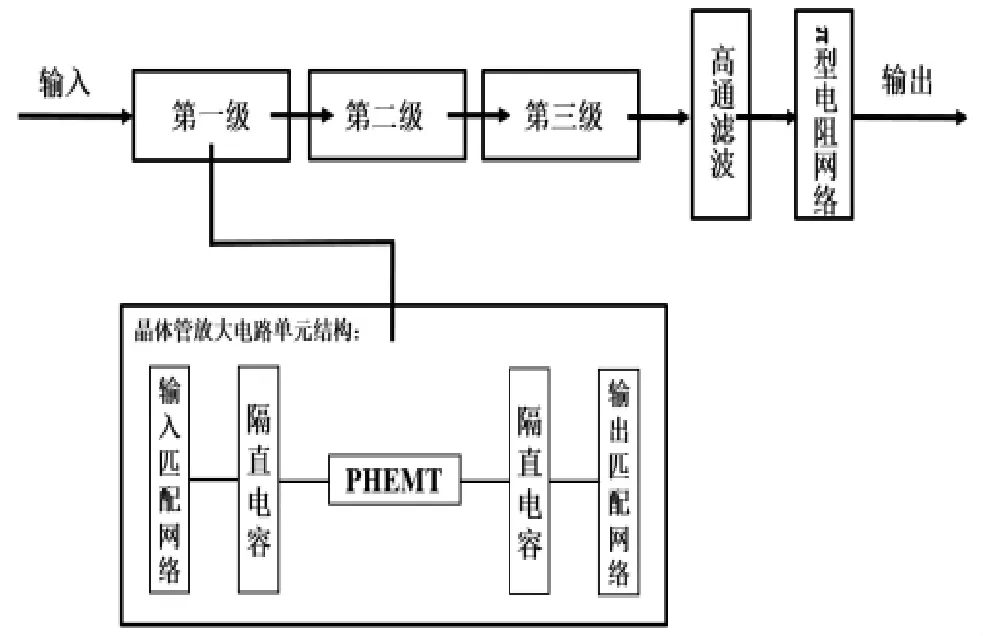

为了使得低噪声放大器在工作频段范围内有较高的增益,采用PHEMT器件三级级联放大的电路结构,每一级晶体管放大电路单元结构相同,整体电路结构如图3所示。每一级晶体管放大电路单元的输入匹配网络可使LNA达到最佳噪声反射系数,每一级电路单元的输出匹配网络,可实现放大电路的高增益和最大传输功率。此外,隔直电容将减少前一级PHEMT器件的漏级电流对后级晶体管栅压的影响。在级联放大链路末级,通过高通滤波器实现带宽内增益平坦度,通过π型电阻网络调节输出驻波比。

图3 晶体管放大电路结构

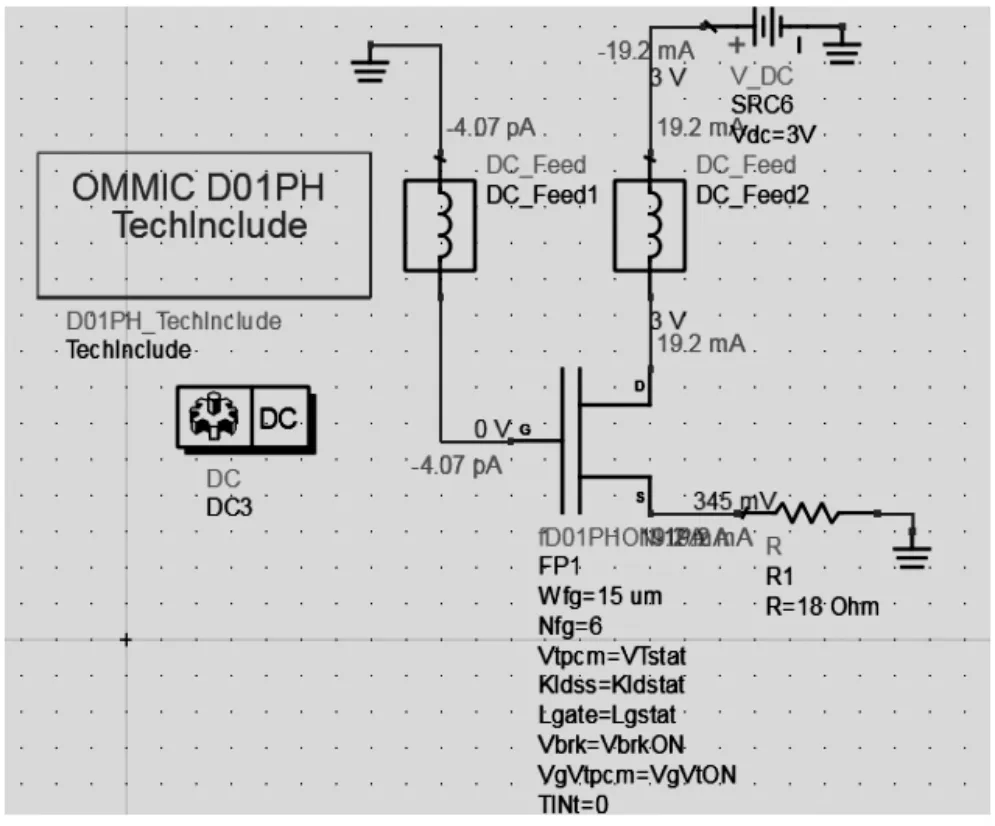

2.2 偏置电路设计

根据PHEMT器件的工作点设计合适的偏置电路。考虑到晶体管的双电源供电需要同时设计漏极偏压电路和栅极偏压电路,增加偏置电路和电源电路的复杂性,因此采用自偏压方式对PHEMT器件供电,自偏压电路如图4所示。漏极偏压电路为PHEMT器件提供稳定的漏极电流与漏压,同时起到隔离射频信号泄露到漏极直流电源的作用。栅极自偏置电路为PHEMT器件提供恒定的栅压,同时遏制漏极到栅极的射频信号。

图4 晶体管自偏压电路

2.3 匹配电路分析

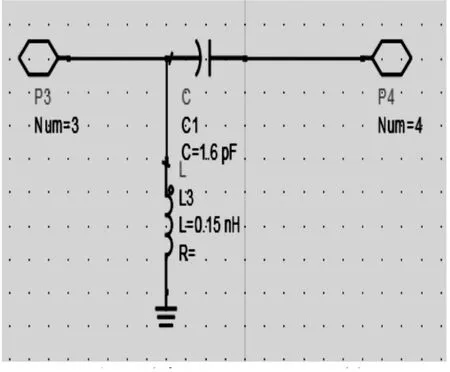

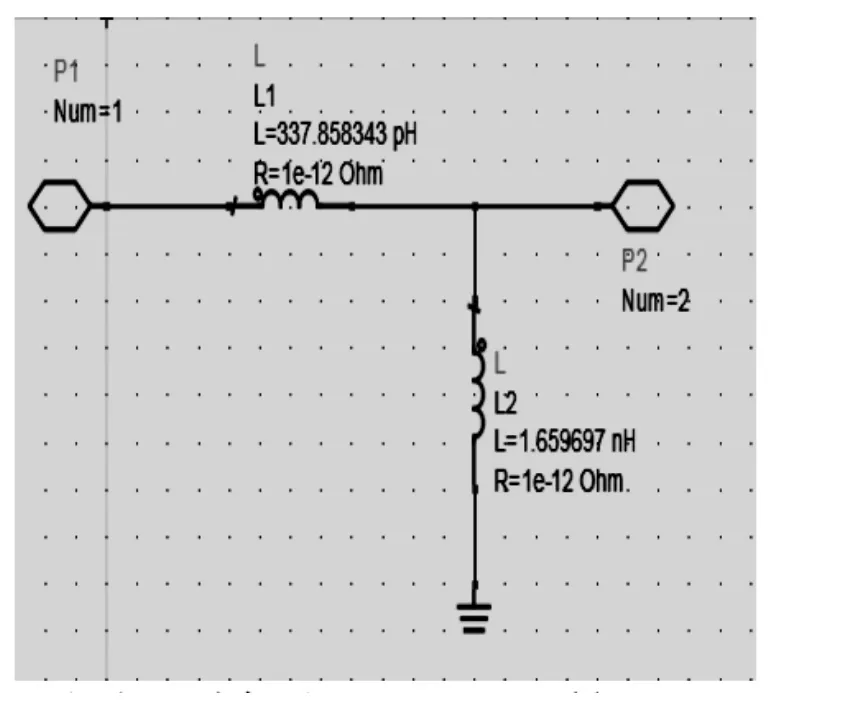

放大器的输入匹配方式主要包括最大功率传输匹配和最小噪声匹配。在低噪声放大器电路设计中,考虑到难以同时实现最小噪声与最大增益的指标性能,因此在电路设计时必须折中考虑,同时兼顾噪声与增益的性能[8]。通常在每一级放大电路的输入端接近最佳噪声匹配,在每一级放大电路的输出端按最大功率传输匹配。本文设计的输入匹配网络、输出匹配网络分别如图5、图6所示,通过仿真得到每一级放大电路输入端呈现的源阻抗以及放大电路在中心频率条件下对应的输出阻抗,用以进行每一级电路的输入、输出匹配。

图5 输入匹配网络

图6 输出匹配网络

图7 晶体管放大电路单元原理图

图8 晶体管放大电路单元的增益图

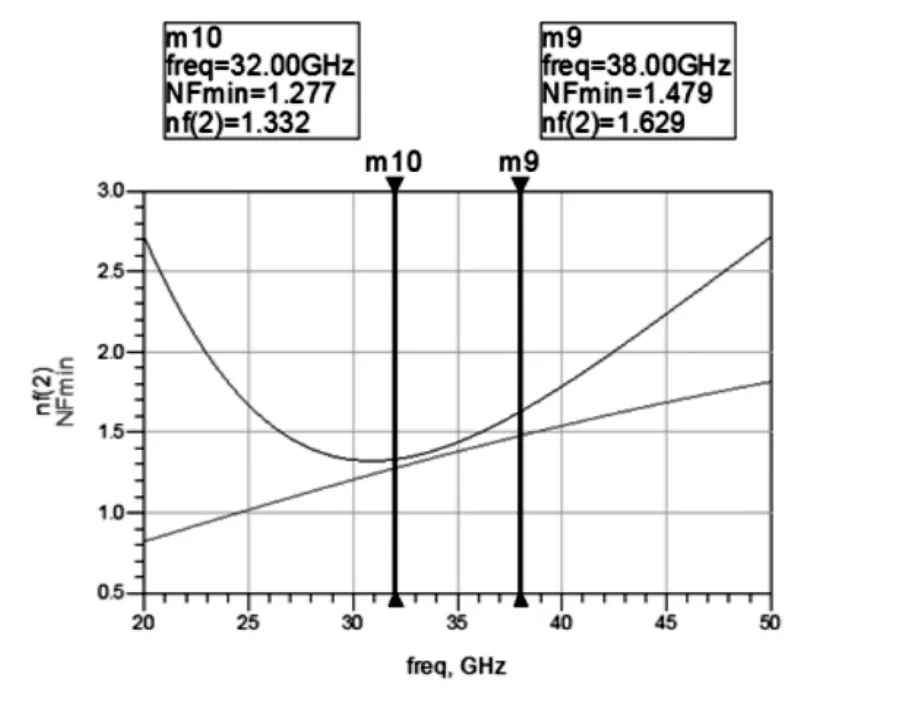

图9 晶体管放大电路单元的噪声系数

2.4 晶体管放大电路单元仿真

本文设计的低噪声放大器采用PHEMT器件三级级联放大的电路结构。针对每一级晶体管放大电路单元进行仿真,并通过调谐多变量优化LNA工作频段范围内的增益平坦度。晶体管放大电路单元原理图如7所示,仿真分析结果如图8、图9所示。

通过仿真分析表明,晶体管放大电路单元在工作频段内的增益范围为7~8 dB,其噪声系数低于1.5 dB。由此可预估PHEMT器件三级级联的电路结构可实现在工作带宽内增益高于21 dB,噪声系数低于4.5 dB。

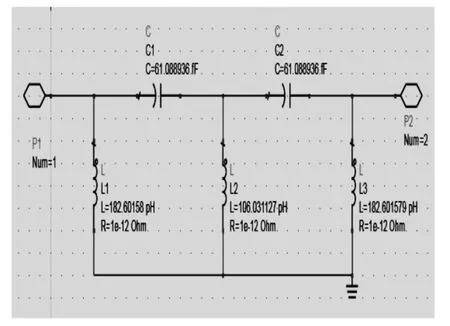

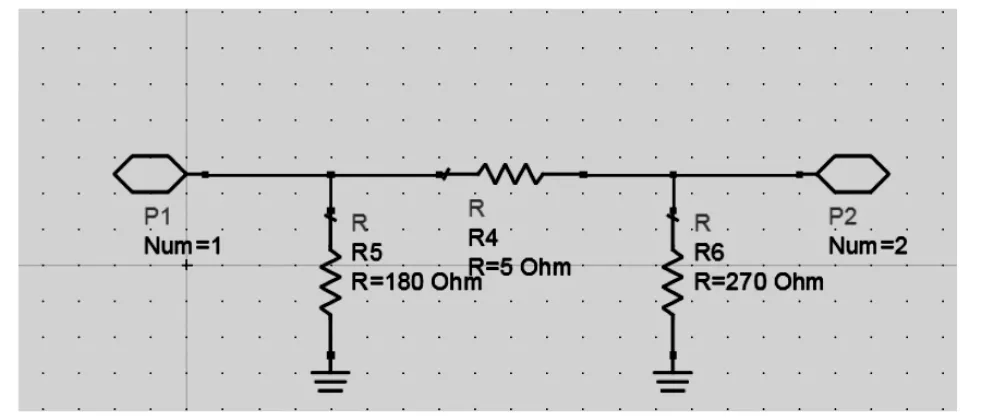

2.5 晶体管放大电路单元仿真

考虑到晶体管放大电路单元在工作频段32~38 GHz范围内的增益不平坦,放大电路单元三级级联之后会导致整体电路的增益平坦度变差,因此在第三级晶体管放大电路单元的输出端串接一个高通滤波电路来提高LNA的增益平坦度。高通滤波器的原理图以及仿真系统生成的滤波器封装模型分别如图10~图11所示。整体三级级联放大电路的输出端串接π型衰减网络调节LNA输出信号的驻波比,其原理如图12所示。

图10 高通滤波器原图

图11 高通滤波器仿真系统生成封装模型

图12 π型衰减网络

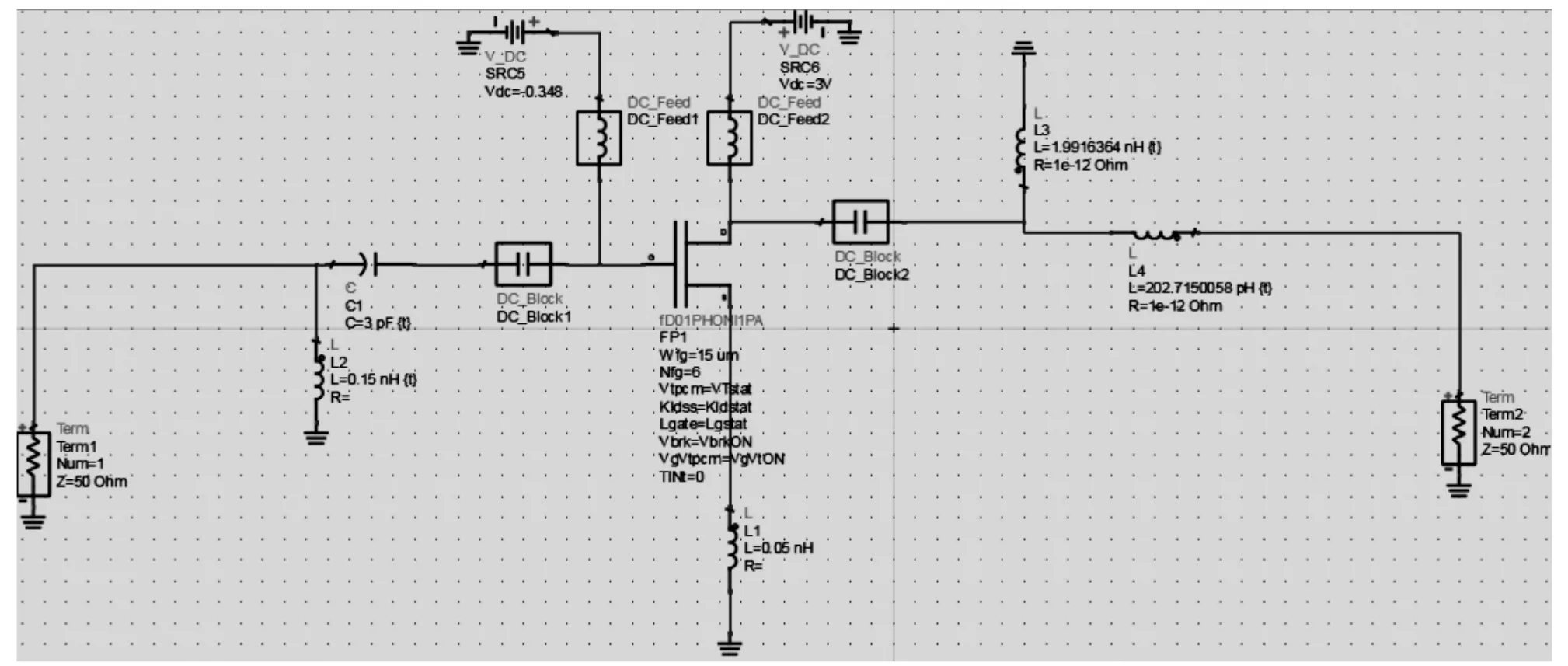

图13 低噪声放大器整体电路级联仿真原理图

3 级联电路仿真设计与结果分析

对低噪声放大器的整体电路进行三级级联仿真和电路参数优化,其电路原理图如图13所示,为较少直流供电电源电路的复杂性,其中每一级的PHEMT器件采用自偏压供电方式。

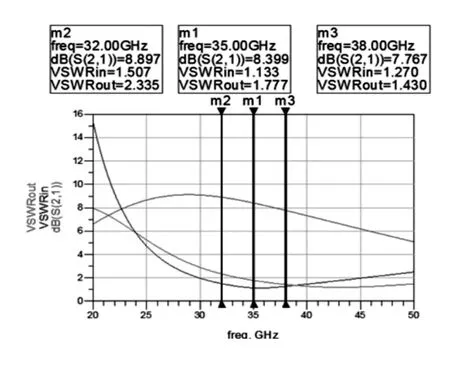

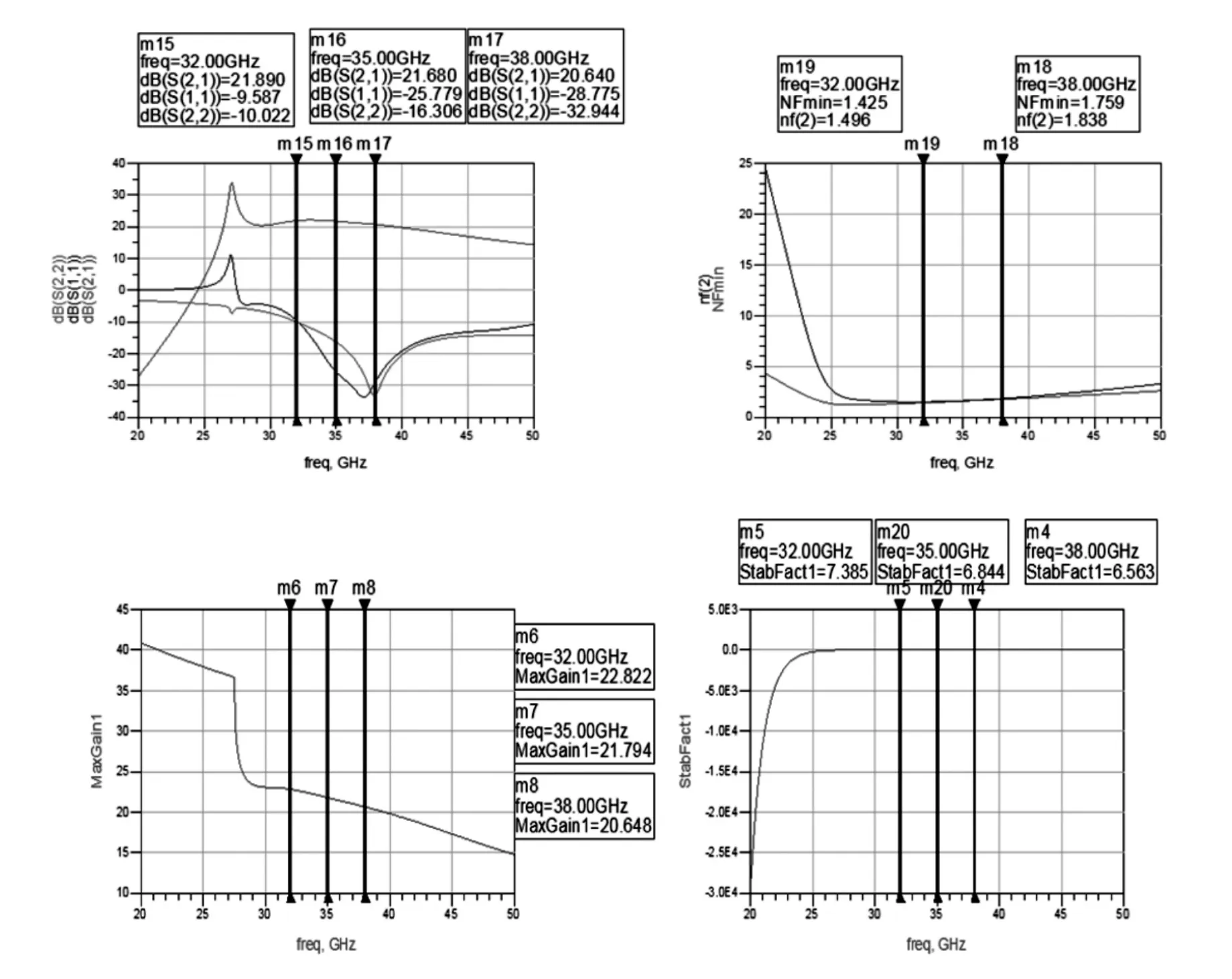

利用计算机仿真优化电路参数后的仿真结果如图14所示。低噪声放大器在32~38 GHz的工作频段范围内,噪声系数NF≤2 dB,带内增益G≥20.5 dB,输入与输出回波损耗RL≤9.5 dB。

图14 低噪声放大器整体电路级联仿真结果

4 结论

本文采用GaAs PHEMT器件研究设计了一款工作频率范围为32~38 GHz的低噪声放大器,该放大器采用赝同晶型高电子迁移率晶体管三级级联的电路结构。为减少偏置电路和直流供电电源电路的复杂性,采用了自偏压供电。通过在每一级晶体管放大电路单元的输入、输出端增加的匹配电路实现得到最佳噪声反射系数、工作带宽内的高增益和最大功率传输。末级电路利用高通滤波提高增益平坦度,同时利用电阻网络调节输出信号驻波比。通过仿真分析表明,该低噪声放大器在32~38 GHz工作频段范围内噪声系数NF≤2 dB,带内增益G≥20.5 dB,输入与输出回波损耗RL≤9.5dB,整体电路设计有着良好性能指标。