行晓曦

(西安卫光科技有限公司,陕西 西安 710065)

功率MOSFET 场效应晶体管具有开关速度快、驱动功率小、安全工作区宽、温度稳定性好等优点,被广泛应用于通讯、计算机、汽车和消费电子领域,并且是分立器件和功率集成电路(SPIC)中的重要组成部分。宇航和卫星用的MOS管与普通MOS管相比[1-2],需要在恶劣的环境中,如宇宙射线、高能离子等辐射环境中工作,因此,在航天器系统设计过程中,需要选择在空间辐射效应中具有最大失效容限的电子部件/器件。航天用的MOS管与国家安全、国民经济全局有一定的相关性,为确保我国航天工程自主创新和跨越发展,必须实现国产化替代。

对管MOSFET 作为一种新型需求器件,与单个MOSFET 产品相比,对管产品在设计之初就就行了性能和功能的匹配,产品同时出现在系统中共同实现一些电气功能,具有很高的市场应用需求。

1 器件工作原理简述

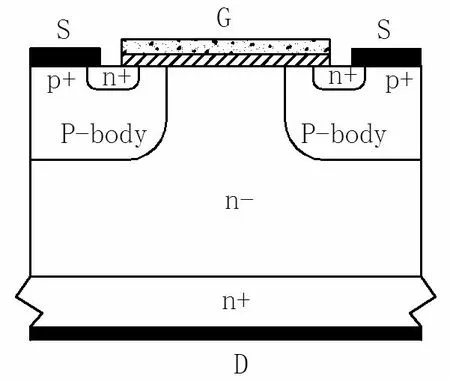

功率MOSFET 器件是电压控制型器件,它是由若干个单元并联组成的,器件的栅极和源极在芯片正面,漏极在芯片背面。图1给出了N沟VDMOS单元结构示意图,给栅极施加栅源电压VGS,当VGS<VGS(th)时,器件未开启,此时漏极电流很小;当VGS≥VGS(th)时,栅极下方Pbody区表面形成了很薄的N型导电层,使漏极和源极之间形成了导电通路,此时器件开始工作,漏极电流增大。功率MOSFET 器件就是通过施加栅源电压VGS使器件在开通和关断之间转换,因此多用于开关电源系统中。

图1 VDMOS 器件的基本结构

2 对管MOSFET 产品方案设计

本文研制产品的管芯设计、流片和封装、测试完全在本单位独立完成,完全自主可控。

管芯是整个产品的关键核心部分,在这里给出管芯设计的主要技术途径。

(1)通过理论计算和软件仿真相结合的方法,首先根据产品的漏源击穿电压,利用非穿通型的经验公式计算出外延电阻率的最小值和厚度的最大值;然后利用穿通型的设计方法,对于一定的击穿电压,存在无限的(WB,ρ B)组合,都可以满足要求,设计中要选取其中一组(WB,ρ B)使导通电阻最小。(2)再根据最大栅源电压计算栅介质层的最小厚度,同时结合阈值电压和其它电参数合理选择栅介质层的厚度和阱注入剂量;最后根据工艺线的最小线宽,确定器件的横向尺寸。(3)把初步计算的结果带入仿真软件的工艺模块,对各个结构和工艺参数进行不断优化设计,以确定最后的流片参数。(4)对仿真优化设计的结果进行流片验证,在流片过程中,要把实际流片结果和仿真结果进行比对,并及时调整,直到生产出合格的产品。(5)整理实际流片的结果,并及时修正仿真软件和算法,以达到仿真和实际生产结果很好的吻合度,最终指导生产,并建立相应的设计文件库。

3 器件设计方面的关键技术

3.1 击穿电压的优化设计。对于低压器件而言,击穿电压要求的达到只要选择好合适的外延层浓度和厚度,耐压都可以达到要求。本文研制对管MOSFET产品终端设计采用场板+沟道截止环相结合的复合终端结构,既可以稳定终端的耐压又可以避免高温漏电不稳定的问题。

3.2 导通电阻的优化设计。对于低压MOSFET 器件,降低导通电阻主要从沟道电阻、接触电阻、衬底电阻、封装电阻几个方面考虑。

3.2.1 降低沟道电阻可以优化阱区的注入剂量,在阈值电压、击穿电压满足要求的前提下,选择较低的注入剂量。

3.2.2 降低接触电阻需要从芯片正面接触、背面接触两方面考虑,芯片正面金属为Al,由于引线孔尺寸较小,必须严格控制刻蚀质量,可以采用过刻蚀技术,避免刻蚀残留,确保正面金属Al 填充接触良好。

3.2.3 芯片背面金属采用Ti+Ni+Ag三层金属,可以保证漏极接触;采用减薄芯片厚度的方式可以有效的降低衬底电阻,根据生产线加工能力,可以将芯片减薄至200um左右。

3.2.4 封装电阻与器件的封装外形有关,在封装形式确定的情况下,可以通过提升封装粘片质量、采用粗丝压焊等方式降低封装电阻。

3.3 开关时间的优化设计。MOSFET电容特性中对开关时间影响最大的就是栅漏电容Cgd,也叫米勒电容。减小Cgd 可以从增加介质层厚度、优化栅极下方的JFET区宽度和减小有源区面积等方面考虑,同时要兼顾阈值电压、击穿电压和导通电阻的要求,需要折中优化设计。

3.4 抗辐照加固技术。为增强器件的抗总剂量能力,我们采用平面栅伪自对准结构,先进行body区的注入及推阱工作,防止推阱的高温过程影响栅氧化层质量,结合阈值电压要求,抗单粒子要求,合理设计栅氧化层厚度[3]。

为增强器件抗单粒子烧毁的要求,增加DP+/DN+注入步骤,减小寄生晶体管基区的电阻Rb,抑制寄生NPN/PNP 晶体管导通造成的烧毁[4]。

4 器件工艺方面的关键技术

4.1 栅氧化层生长工艺。器件具有抗辐照要求,所以,对器件栅氧化层质量要求就特别高,采取技术措施:

4.1.1 采用平面栅伪自对准工艺,避免栅介质层经历高温过程。常规自对准工艺栅介质层生长之后,会经历长时间的高温退火过程,高温推火会在氧化层中形成断裂键,这种缺陷在总剂量辐照过程中会导致阈值电压漂移、漏电增加、甚至栅氧化层破坏的问题。我们使用平面栅伪自对准工艺,可以避免这种情况的发生。

4.1.2 进行高质量栅氧化层生长技术,采用上述的平面栅伪自对准工艺,即先形成主结区,再进行薄栅介质层生长,氧化层的结构为干氧+湿氧+干氧的结构,在工艺过程中严格控制氧化层中正电荷栅的数量,以达到控制氧化层质量的目的。栅氧化层生长之后直接进行900℃的N2 退火工艺,可以提升栅氧化层质量,提升抗总剂量能力。

4.1.3 采用栅介质层工艺设计,采用低温氧化+N2退火的工艺。栅氧生长采取850℃低温生长,900℃氮气退火工艺。

4.2 隔离介质的稳定性。常规MOSFET 器件一般采用USG+BPSG材料作为栅源之间隔离介质,但对于具有抗辐照要求的特殊器件,隔离介质需要在重粒子辐照作用下,仍然能够承受一定的栅源电压,避免介质击穿,造成器件失效。而BPSG材料在重粒子辐照下会使材料内部的缺陷增加,从而影响栅源击穿电压及器件的抗辐照能力,因此抗辐照MOSFET 隔离介质仅采用USG。

4.3 小尺寸引线孔金属填充工艺。器件孔刻蚀采用先湿法再干法的方式,形成上宽下窄的孔形貌,便于后续金属填充,同时过刻0.2um,防止刻蚀残留造成接触不良。另外,在Al 填充之前,先溅射一层薄的Ti/TiN膜,可作为湿润层,有利于Al 膜的流动,确保孔金属填充充分。

5 对管MOSFET 器件仿真

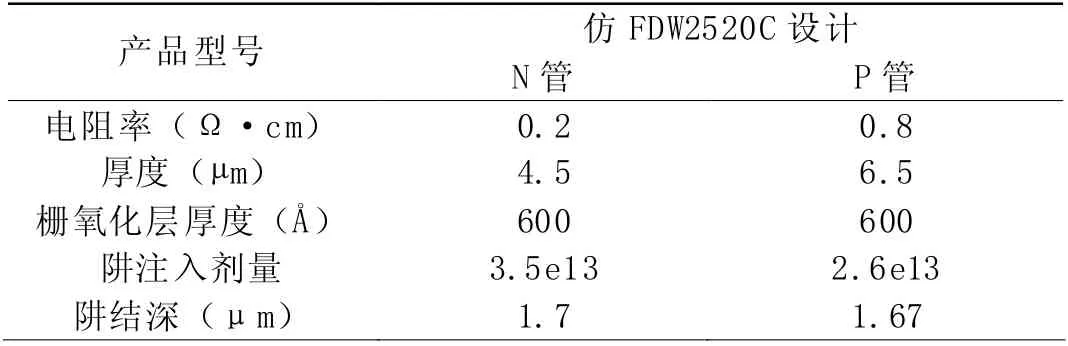

本文产品结合工艺线实际情况,采用条形单元结构,因为条形设计避免了单元设计中固有的角效应,提高了栅极氧化物的质量可控性,并且易于制造。源区宽度利用仿真软件进行优化设计,综合考虑导通电阻、开关时间和芯片面积等,最终确定元胞尺寸为8.4μ m,栅宽4μ m,N+1μ m,P+2.4μ m,DP+3.4μ m,孔2.4μ m。芯片设计结果见表1。

表1 对管MOSFET 管芯设计结果

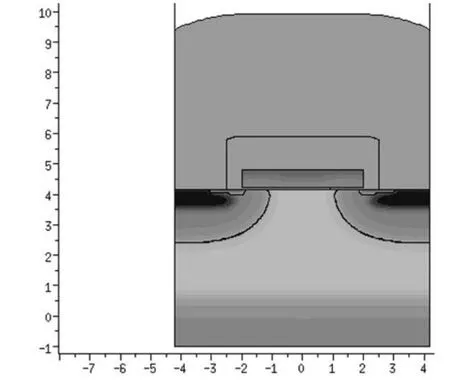

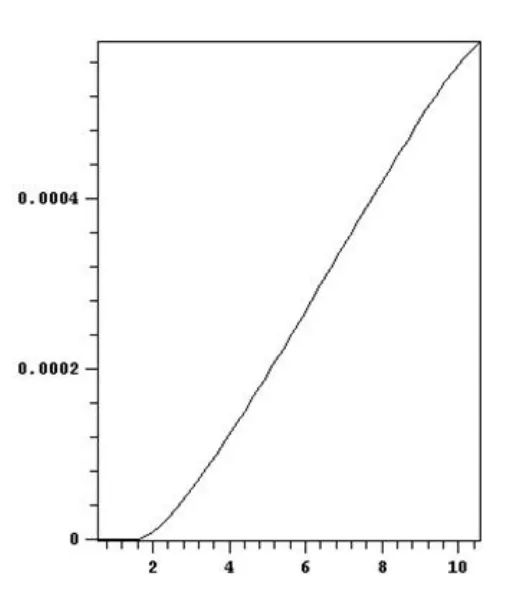

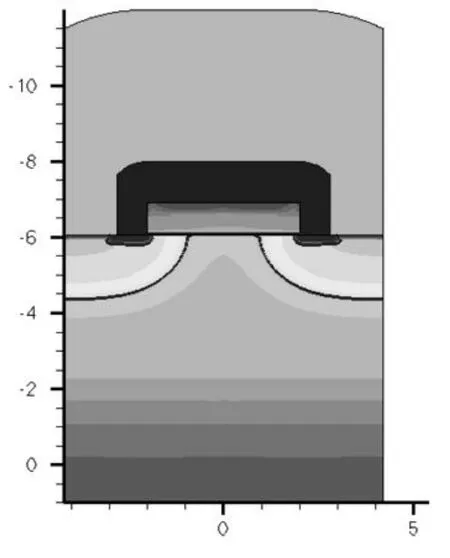

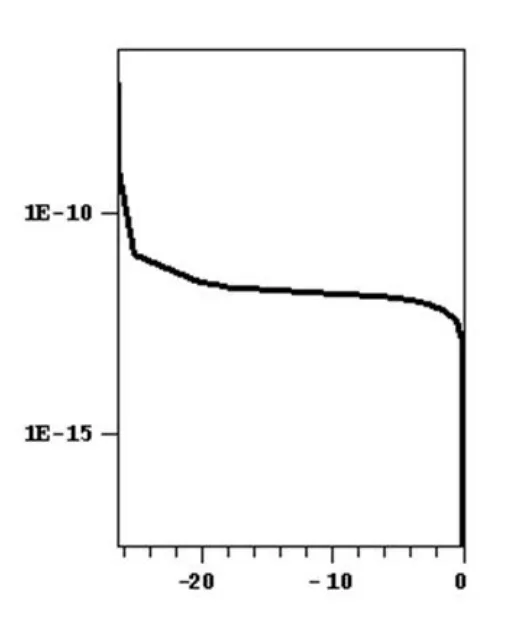

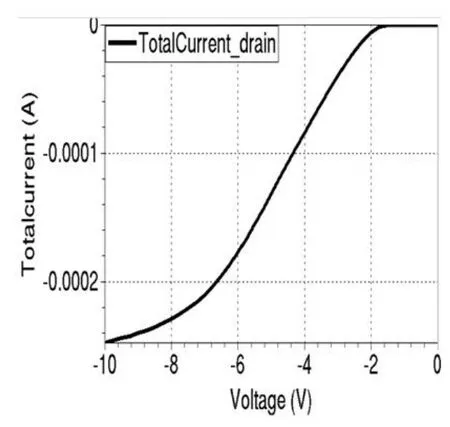

器件仿真结果均达到了设计要求。对管N沟:器件的工艺仿真结果如图2 所示;从图3 击穿电压的仿真结果可以看出BVDSS=44.6V;从图4 阈值电压的仿真结果可以看出Vth=1.6V。对管P 沟:器件的工艺仿真结果如图5 所示;从图6 击穿电压的仿真结果可以看出BVDSS=-28V;从图7 阈值电压的仿真结果可以看出Vth=-1.63V。结果均满足设计要求。

图2 N 沟器件工艺结构

图3 N 沟击穿电压仿真结果

图4 N 沟阈值电压仿真结果

图5 P 沟器件工艺结构

图6 P 沟击穿电压仿真结果

图7 P 沟阈值电压仿真结果

沟道的宽度由元胞数目确定:

W=L× N (N=(RC/L)/Ron)

其中:W 为沟道宽度,L 为条形元胞条长,N 为元胞数目,RC/L为条形单胞导通电阻,RC由仿真值确定,Ron为器件导通电阻。元胞导通电阻是通过ISE 软件仿真得到。器件导通电阻是设计时的要求值,由于在仿真过程中忽略了衬底及封装电阻,所以在导通电阻计算过程中要给出约30%的设计余量。对管产品设计了相同的芯片面积,综合各种技术要求,本文研制对管产品最终设计的芯片总面积为4.2mm× 3.5mm。

6 流片工艺流程

在本对管产品研制的实施中,根据产品的性能指标要求,加工工艺生产线的具体情况,N沟产品制定管芯工艺流程如下:

N+硅衬底外延片→生长场氧→光刻场限环和有源区(一次光刻)→生长牺牲氧化层→光刻p-body区(二次光刻)→P-body和场限环注入/退火→生长薄栅氧化层→CVD 淀积多晶硅、多晶掺杂→多晶光刻(三次光刻)→去除多余残氧→源N+光刻(四次光刻)→N+注入→DP+光刻(五次光刻)→DP+注入→源P+光刻(六次光刻)→PSD注入→激活→USG淀积→一次致密→孔刻蚀(七次光刻)→二次致密→溅射Ti/TiN→溅射金属Al→金属光刻(八次光刻)→硅铝合金→USG 淀积→氮化硅淀积→钝化层光刻(九次光刻)→背面减薄→背面金属化→CP 测试。

对管P 沟产品管芯工艺流程与N沟相似,对于对管MOSFET做版图设计时考虑做了一致的版图,进行流片时候即采用相同的光刻版,具体流片工艺条件根据N沟、P 沟产品各自的工艺方案具体实施。

7 产品封装筛选工艺流程

根据用户和技术协议要求, 对管采用SMD-0.5 金属扁平封装,N、P 沟道产品封装筛选工艺流程如下:

烧结→压焊→平行封焊→高温存储→温度循环→热响应→恒定加速度→PIND→密封→稳态栅偏置→功率老练→三温测试→目检

8 工艺主要考核项目及试验情况

8.1 管芯部分

管芯工艺主要考核项目为:栅氧化、N+注入、源P+注入进行控制,最终管芯测试,电参数按要求进行测试,测试合格率达到98%以上。

8.2 产品后部封装部分

后部封装工艺主要考核项目为:烧结质量、键合强度、密封性,内部水汽含量控制、电性能参数。电性能参数主要以测试为依据,测试合格率达到95%以上。

9 产品测试结果与讨论

对管产品6A/20V、-4.4A/-20V的器件流片测试结果与国外同类产品的对比可以看出:(1)所设计对管MOSFET产品在静态参数和动态参数方面均达到了国外同类型产品特性指标;(2)所设计对管MOSFET产品在抗单粒子和抗电离总剂量方面均达到了国外同类产品水平;(3)所设计对管MOSFET 产品漏极截止电流均在60nA以下,小于国外产品要求的1μ A;(4)所设计对管产品开关时间典型值均优于国外同类产品;电容和栅电荷基本达到了国外产品典型值水平。

10 结论

本文介绍了MOSFET器件的工作原理,重点研究了低压、低阈值且具有抗辐照特性的对管MOSFET 设计和工艺关键技术。研究的6A/20V、-4.4A/-20V性能指标达到设计要求,可以功能替代国外型号FDW2520C,且增加了抗辐照性能,可以应用于航空、航天领域的电源系统。