周敏杰

(安费诺电子装配(厦门)有限公司,福建厦门 361009)

0.引言

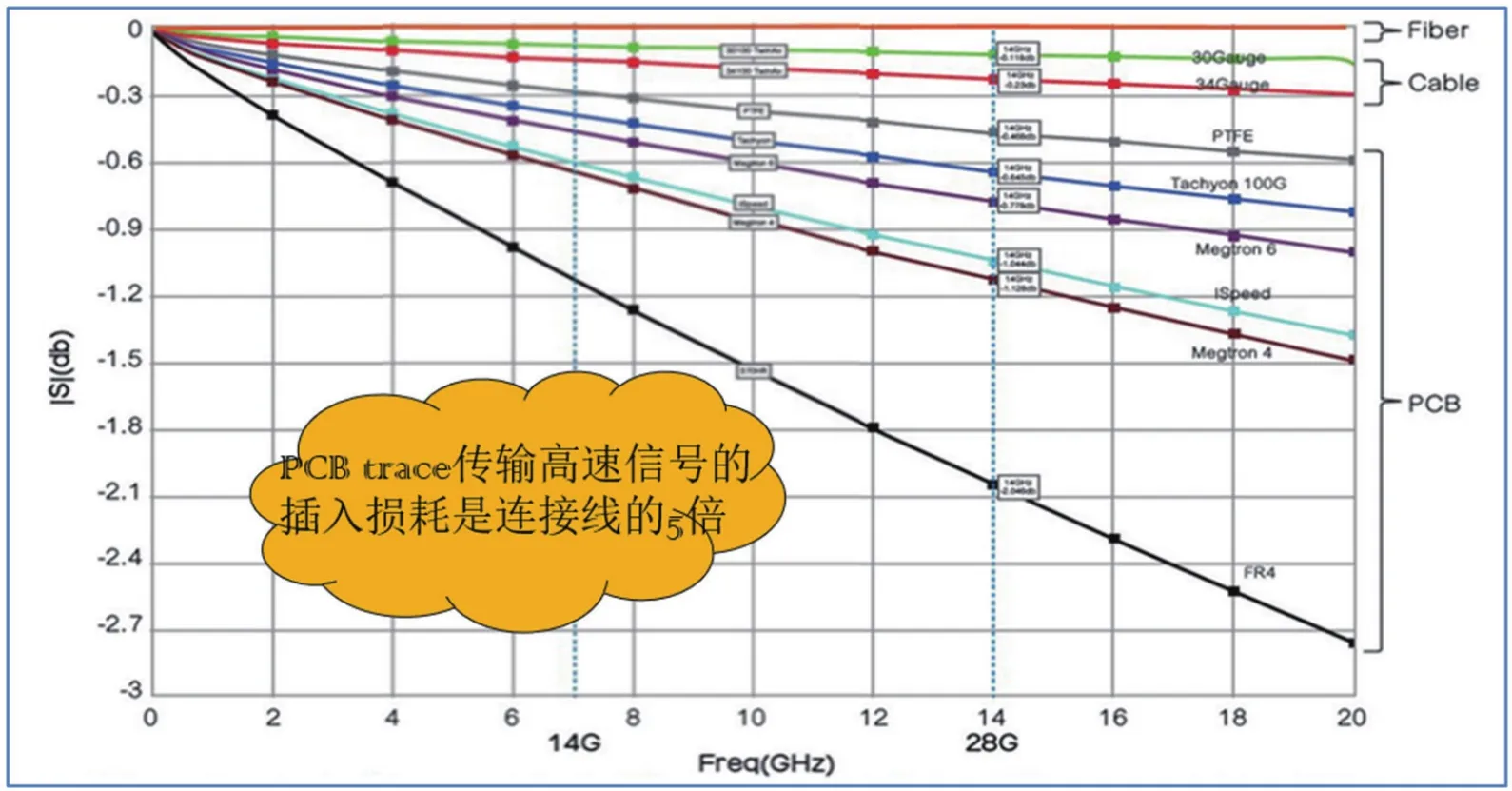

在PCIe5.0之前,服务器内部几乎所有的高速信号都是采用PCB走线的方式去连接,采用的方式基本就是主板+背板的方式,结构清晰,能够满足信号的要求。但是速率来到PCIe5.0之后,PCB走线的插入损耗大大增加,原因在于基础频率又从原来的8GHz(PCIe4.0)直接扩大到16GHz,这就使得原本符合PCIe4.0的系统要求,却再也无法满足PCIe5.0的要求,急需要解决的问题就是高速通道的信号插入损耗过大问题。针对这个问题,安费诺公司提出采用内部线缆的方案去实现。因为线缆的插入损耗要远小于PCB走线,通常情况下,采用线缆方案的插入损耗只有PCB走线的1/5,可以参考图1。至此,Riser card线缆方案应运而生,而传统的Riser card方案是没有线缆的,同时高速线缆方案也是几乎不放置电子元件的,于是这一创新方案必然会带来更多的挑战。

图1 PCB trace与线缆的插入损耗对比图

本文就是基于这2个方面的融合所产生的问题,对与线缆有关的过孔和焊盘而做的总结,并推荐一个可行的PCB设计方案,为后来的设计者提供参考。

1.Riser card线缆结构

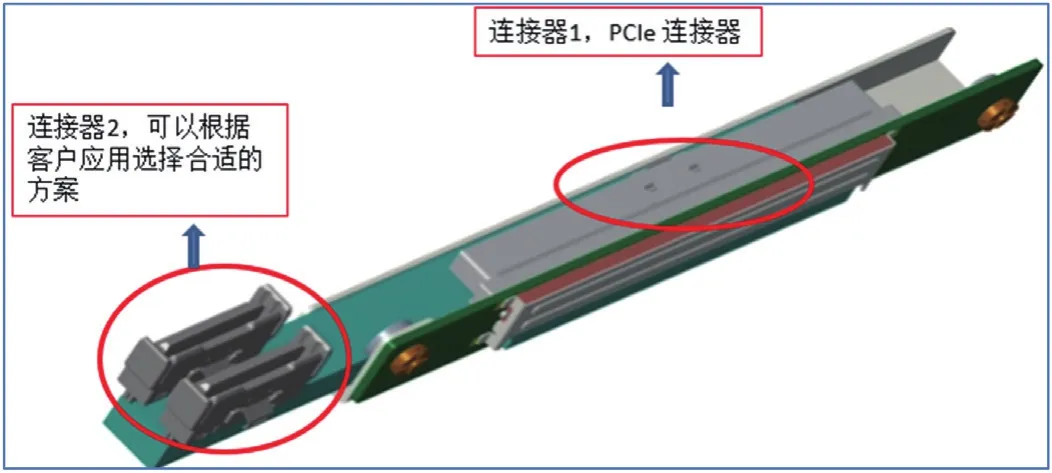

Riser card的线缆结构如图2所示。它的内部组成为CEM连接器+PCBA+Raw Cable+PCBA+连接器2,其中连接器2可以根据客户需求选用不同的方案。

图2 Riser card线缆图示

2.Riser card线缆PCBA阻抗设计

高速信号传输的一个重要参数就是阻抗匹配,如果阻抗匹配得好,其他参数都会变好,如ILD会更平稳、回波损耗会更小等。一般而言,Riser card的PCBA阻抗管控的好坏直接决定了这条线缆的性能,而影响Riser card PCBA的阻抗连续性主要有5个关键区域:

(1)高速连接器本身的阻抗;(2)高速连接器的SMT区域;(3)PCBA板上走线的区域;(4)PCBA过孔区域;(5)PCBA 焊盘区域。

2.1 Riser Card线缆PCBA过孔设计

细分以上总结的5大影响阻抗的区域,连接器本身阻抗以及SMT区域与PCB设计关系不大,而PCB走线也比较容易管控。传统的Riser card与线缆方案的Riser card区别也恰恰在于过孔设计和线缆的焊盘设计,首先看过孔设计。

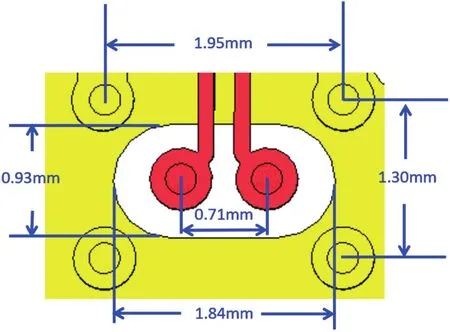

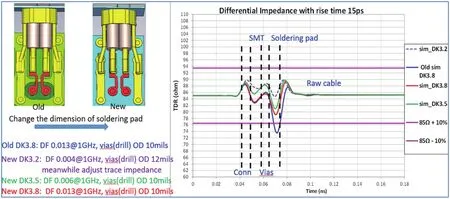

这里的过孔指的是靠近线缆焊盘的过孔,因容易受到线缆焊接的影响,会跟以往的设计不同。根据仿真结果,过孔之间的中心距与中心距的值在0.7mm~0.76mm最佳,过孔的直径可以选择10mils或者12mils,而最佳搭配可以参考PCB材料的DK值。过孔的尺寸可以参考图3。

图3 过孔及相关的避空尺寸

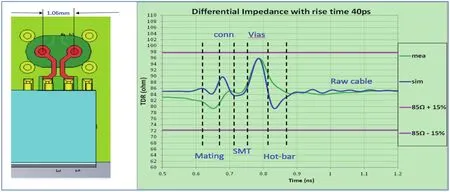

如下是采用和不采用推荐的过孔直径仿真结果、实测结果对比,如图4(非推荐尺寸)和图5(优化成推荐尺寸)所示。

图4 采用过孔间距1.06mm的设计仿真和实测对比

图5 按照推荐尺寸的仿真结果

2.2 Riser card PCBA焊盘设计

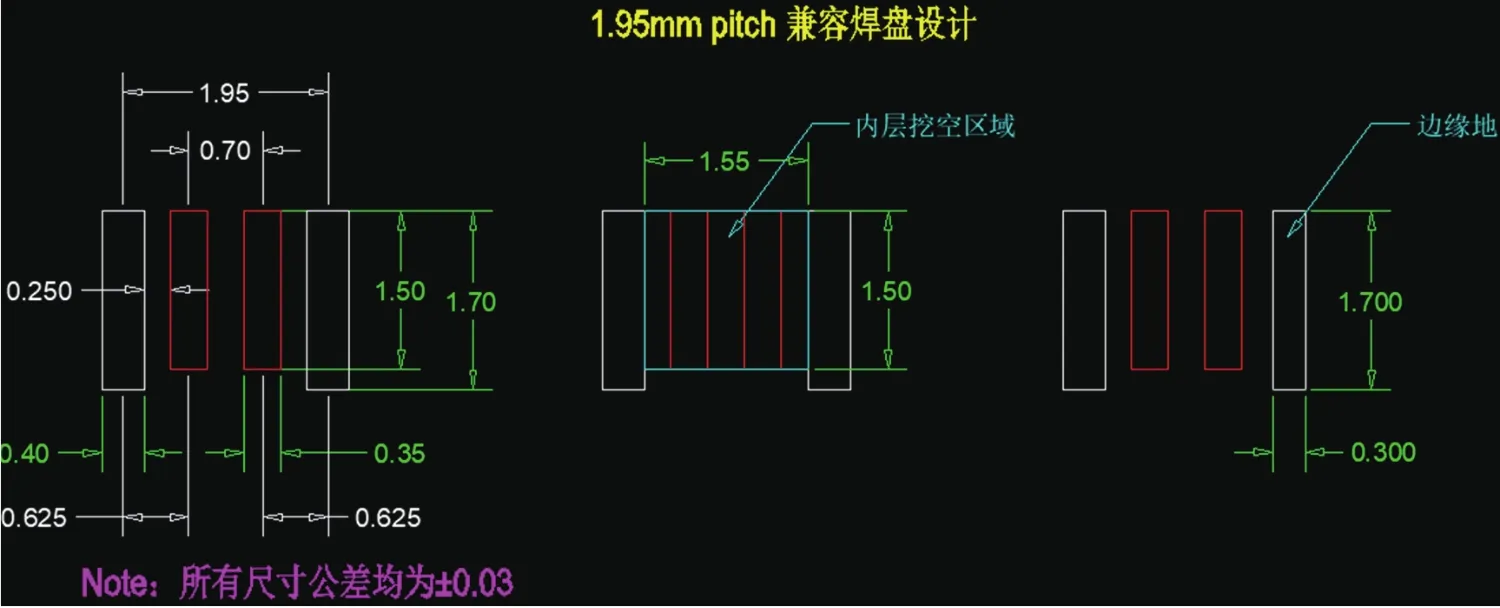

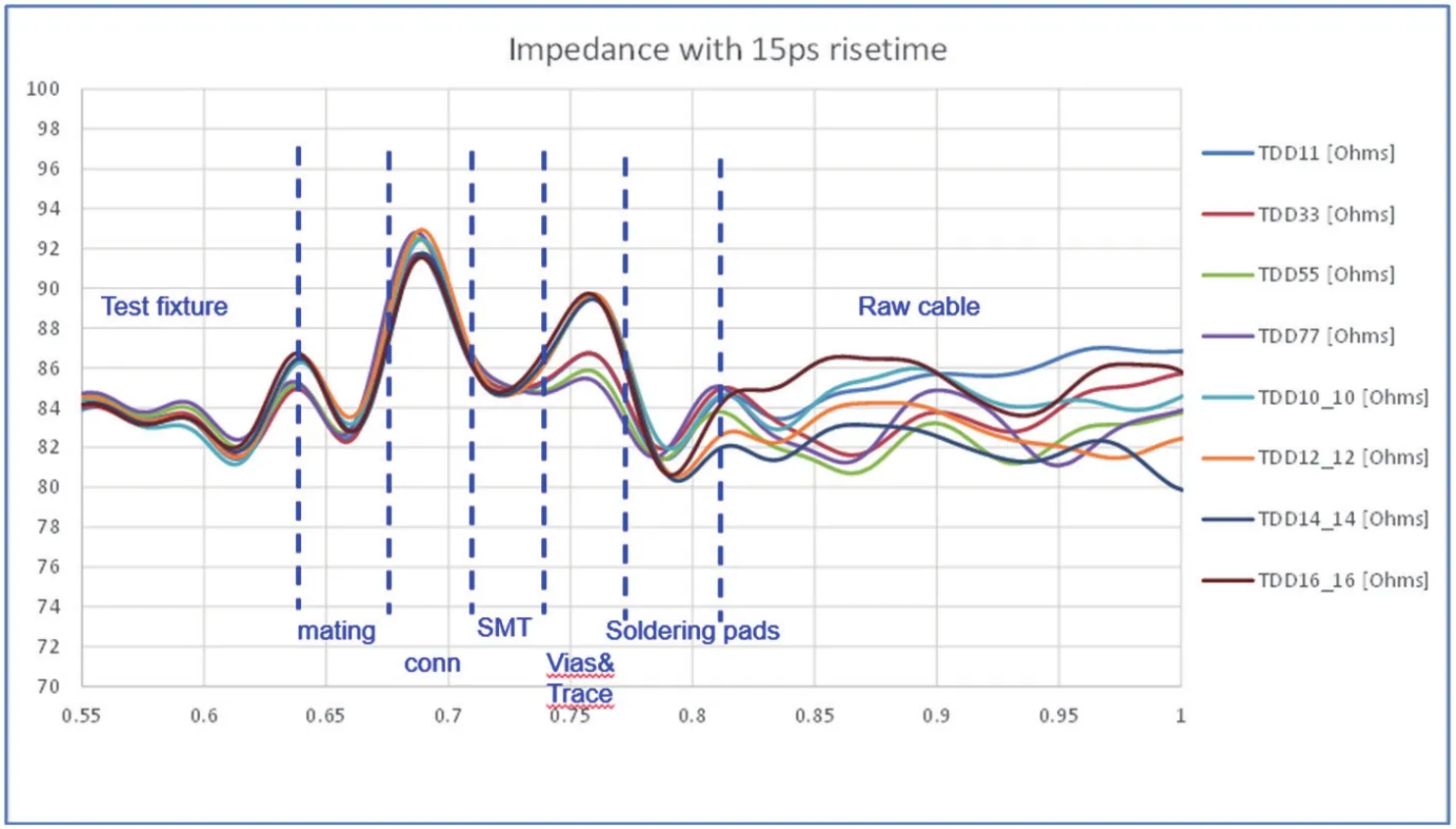

针对PCBA焊接区域,要考虑焊线、涂UV胶及内模工序会使该区域的阻抗下降。因此,设计时需同时考虑该区域焊盘区域的阻抗线材、UV胶及内模综合因素等。经过多次的实验和仿真,推荐焊盘尺寸如图6所示。同时给出仿真数据,采用不同的PCB材料、不同的过孔尺寸所做的一个结果对比,如图7所示。

图6 焊线焊盘的推荐尺寸

图7 经过焊线、涂UV胶及内模工序后的仿真(已隐藏UV胶和内模部分)

以上结果是基于仿真的结果,而焊盘区域的阻抗还与制程密切相关,如焊点锡量过大,就会导致阻抗偏低很多。所以对于PCIe5.0的应用,最好推荐DK相对较低的材料,并结合焊点较理想制程管控才能得到合格的SI要求。如下实测的阻抗曲线图可供参考,如图8所示。

图8 实测阻抗曲线图

3.结语

本文提出通过CST仿真软件,结合Riser card线缆实测数据,模拟仿真Riser card PCBA阻抗与实测数据的对比,并推荐出PCIe5.0 Riser card线缆方案的PCBA设计方案,重点推荐了高速信号在焊盘附近的过孔尺寸,以及焊线焊盘的尺寸。参考此方面的设计经验,可以大大缩小开发时间,因此可以避开传统Riser card与线缆Riser card的设计不同而导致系统调试失败。线缆Riser card是一种传统高速线缆与传统的Riser card的技术融合。