严健生,杨柳青

(中国科学院微小卫星创新研究院,上海 201203)

1 概述

宇宙高能粒子(太阳宇宙线或银河宇宙线)射入半导体器件SRAM 单元灵敏区时可使器件逻辑状态翻转,导致系统功能紊乱。这种单粒子翻转(SEU)造成的逻辑错误不是永久性的,一般不会造成器件的物理性损伤。SEU已经成为卫星电子设备的常见错误。

目前大多数FPGA 基于SRAM 结构。SRAM 型FPGA的用户组合和时序逻辑都是用可配置的存储单元(即SRAM 单元)实施。根据SRAM 的结构特点和SEU 产生的机理,SRAM 是FPGA 中最容易产生翻转的部分。随着集成电路工艺向低电压、高集成度方向发展,相应的空间SEU 阈值越来越低,因此FPGA 发生故障的概率越来越高,最终导致计算结果错误、程序执行任务系列错误、数据域改变、程序指令错误导致系统跑飞异常复位、甚至导致卫星相关系统永久失效、烧毁。因此针对SRAM 型FPGA 很有必要进行高可靠性设计。

针对SRAM 型FPGA 的特点,本文分别从硬件设计角度和软件设计方面对SRAM 型FPGA 设计提出可靠性设计。

2 可靠性硬件设计

2.1 选用抗SEU 器件是根本办法

衡量器件抗SEU 能力是用该器件的翻转阈值和翻转截面来描述的。由该器件的翻转截面对线性能力传递(LET)值的曲线可以推算出卫星轨道的SEU 翻转率,用次/天·位表示。整机设计时选用SEU 率低的器件非常重要,如果SEU 率非常高,其它的措施都将不起作用。

2.2 整体屏蔽减少辐射效应

整体屏蔽办法就是在卫星电子设备外面包覆一层具有一定厚度的屏蔽材料,通常采用的材料有铝、铅、钽和某些酯类化合物等,此法可以有效地缓解卫星电子设备所承受的空间辐射压力,减少空间辐射环境对电子设备造成影响。

2.3 器件级加固

在制作FPGA 芯片时采取抗辐照工艺及其它硬件加固手段,增强芯片本身对空间辐照环境的耐受力。

2.4 应用纠错电路EDAC

错误检测和纠正电路(Error Detection and Correctio n,EDAC)可以纠正SRAM 型FPGA 数据中的一位错误和检测出两位错误能力。其原理是:处理器向FPGA 内部RAM 存储区域写入数据时,根据写入的数据生成一个变形汉明码校验字例如(7,4)汉明码,把该校验字存入RAM 存储区中。当下次处理器读取该区域数据时,同时把数据和相应的校验字同时送入EDAC 电路中进行纠错,若EDAC 电路发现检测数据中有一比特数据出现错误时便生成单错标志SEF,并输出纠正后的数据和校验字。若同时出现两比特以上数据错误时,EDAC 电路不能纠正数据错误,只产生双错标志DEF。在某些情况下在软件设计中必须要考虑SEU 造成两位或多位翻转。

版图交错法就是一种有效降低单粒子多位翻转影响的方法[1]。其方法是将同一逻辑码字中的各比特位放置到存储器的不同物理位置上,当单粒子多位翻转时,实际上翻转的比特位在逻辑上是分离的,因而可以被纠错。

2.5 硬件冗余

使用多个SRAM 型FPGA 同时运行相同的程序,并将某一时刻运算的结果同时输出给抗辐照加固器件中进行仲裁,以达到纠错目的,该方法可靠度较高,因为需要多个FPGA 同时运算和表决因此会带来较大的功耗和硬件开销。

3 可靠性软件设计

3.1 重新配置FPGA

对FPGA 进行重新配置可以清除累积错误。在估计的SEU 发生间隔时间内重新配置FPGA ,潜在的SEU影响可以被抑制。翻转的配置信息在重配置时可以将翻转的配置位纠正。

在重新配置期间,FPGA 不处于工作状态,并且器件管脚也会处于一种不受控状态,所以需要在系统层面充分考虑FPGA 重新配置期间地保护与重新配置后地恢复处理,设置合适地时机启动重新配置操作。实际应用中在低辐照的空间环境或者对于可以短时工作的卫星设备或载荷设备可以运用此方法,如按需工作的CCD 成像仪等[2]。

3.2 配置刷新

配置刷新就是在不中断当前功能和逻辑的基础上重新写入配置数据。一般情况下配置刷新需要FPGA 外部设计相应的控制电路,如ASIC、反熔丝FPGA 或微处理。而Xilinx 公司的Virtex-5 系列以上FPGA 集成了配置存储区内部回读纠错技术,不需要板级额外增加控制电路,简化了系统设计。配置刷新有回读刷新和定时刷新两种方式[3]。

(1)回读刷新

第一种方法是回读对比配置区数据帧,与初始的配置数据进行对比,如果对比数据不一致,则对该帧进行刷新,刷新以帧为最小单位。该方法需要使用固化(.msk)和回读文件(.rbb),这两个文件大小都与FPGA 配置的原始文件大小差不多,因此本方法对系统存储区要求较大。

一般电路中会使用一片高等级的具有抗单粒子免疫的FPGA 例如Actel FPGA(反熔丝工艺,对SEU 免疫)作为具有检测和监督功能的芯片,通过反熔丝FPGA 不断的回读SRAM 型FPGA 内部的配置文件并进行校验,一旦发现校验出错,就自主控制拉低PROM 配置引脚,重新加载FPGA 配置文件,通过更新配置文件来确保FPGA一直处于配置正确状态。由于配置文件包含的是FPGA所有资源的配置信息,其中包含设计中未使用的一些模块。而这些模块的资源配置信息如果遇到单粒子效应其并不会影响FPGA 的正常功能使用,然而这些冗余的配置信息往往占整体信息比例较高会严重降低校验的效率,因此增加一片PROM 芯片存放屏蔽位文件,该文件专门对设计中未被使用资源的配置信息进行标注。通过对该文件的分析,可以仅对设计中使用资源的配置信息做校验。

第二种方法是回读对比配置区数据帧CRC 校验结果,与存储的初始CRC 校验结果进行比对,如果结果不一致,则对出错帧进行刷新。本方法只需存储CRC 校验结果,对系统存储区的需求很小。

回读FPGA 配置文件有两种模式,一种SelectMAP模式,另一种为边界扫描(JointTestActionGroup,JTAG)模式。SelectMAP 模式采用并行模式读取数据,读配置文件的速度较快,但采用该模式FPGA 的某些通用引脚必须作为SelectMAP 模式的数据读取专用引脚,FPGA 引脚被占用得比较多。而JTAG 模式采用串行模式读取数据,虽然读配置文件的时间比较长(采用1MHz 的时钟,回读配置文件的时间为2s 左右),但FPGA 被占用的引脚仅为4 个。

Xilinx 7 系列FPGA 发布的SEM IP 具备纠正SEU软错误的能力[4],其替换模式基于数据重载的修复方式,支持任意多个比特错误。SEM IP 能实现FPGA 内部配置区文件与外部FLASH 内存储的EBC 文件的比对,并对配置区进行刷新。

(2)定时刷新

定时刷新指的是在特定程序的控制之下,或者以一定的时间周期例如卫星星历表的时间信息在指定的时间来对FPGA 的配置文件进行重加载操作,FPGA 重新加载程序可以有效避免因为SEU 效应而对单机或系统而产生影响,定时刷新过程在设计的时间点上应不影响用户正常功能的使用。该方法的优点是在不增加硬件开销成本的基础上只需要通过软件编程即可实现,具有较高的灵活性和经济性。例如在现有的商业卫星测控系统中,为了避免卫星在入境时存在SEU 效应,一般的在卫星入境之前五分钟,卫星计算机系统会发出刷新指令对测控系统中的FPGA 做一次全面的刷新操作,保证卫星在进入测控通信弧段之前测控系统无SEU 影响。

回读刷新一般采用反熔丝FPGA 作为控制器对刷新过程进行控制,其软硬件设计较为复杂。相较而言,定时刷新器件自动识别和匹配目标FPGA 芯片,只需提供时钟和刷新使能信号,即可自动实现对目标FPGA 的刷新操作,大幅降低系统设计的难度和复杂度,缩短开发周期。而回读刷新只在发现翻转错误时进行刷新,故障恢复更加高效和有针对性。

3.3 三模冗余

对关键数据或信号进行三模冗余(TMR)设计能有效防止SEU。TMR 是利用3 个相同单元构成并联形式,通过表决单元输出最终的数据或信号。在一个单元发生SEU 的情况下,通过表决,保证了关键数据或信号的正确性和安全可靠。TMR 在提高可靠性的同时,也会需要开销额外的资源和速度降低系统的性能,而表决器本身也不是完全可靠的,并不具备抗空间辐照的能力。如果一个长加电系统长时间暴露于空间辐照环境中,由于SEU 的累积效应,两个表决单元发生SEU 的可能是存在的,在这种情况下三模冗余失效。

在传统三模冗余技术的基础上引入反馈路径可以解决因为SEU 错误累积而导致的三模冗余失效问题,利用当前的正确判决结果对前一级的冗余寄存器进行更新,从而及时纠正前级可能引入的SEU 错误,避免错误的累积。对于那些不断更新数据的寄存器,即便发生SEU 错误,在下一个时钟周期内就会被新的数据覆盖,因此这种寄存器冗余采用传统三模冗余即可;对于那些长时间驻留的数据寄存器建议采用反馈纠错的三模冗余[5]。

3.4 回读刷新结合三模冗余

为了更有效的提高FPGA 抗空间辐射的更有效方法,国际上主流的做法是采用回读刷新结合三模冗余方法,此方法可以增强SRAM 型FPGA 的抗SEU 能力。

3.5 动态局部重构

回读刷新和定时刷新需要对FPGA 进行全面的配置,然而一些设备需要长时间稳定工作,整体的刷新会影响到他的性能,针对这些系统往往采用动态局部重构。动态局部重构是指对于被规定为可重构区域内的硬件逻辑资源可进行实时的动态重构操作,而其它部分的电路逻辑功能不会受到影响。动态局部重构要求FPGA 具有动态局部可重构能力。只需将FPGA 中的部分逻辑或模块的配置信息进行动态重新配置,不需要重新加载整个FPGA 的配置文件,非重构部分的工作状态完全不受影响。FPGA 动态局部重构技术首先由Xinlinx 公司提出和实现,目前Xilinx 公司很多系列的FPGA 芯片支持动态局部可重构技术。动态局部重构技术可以有不同的设计流程[6]。

针对局部动态重构技术的特性,可以充分利用局部动态重构技术在保证工作状态的功能不受影响的情况下局部重构被单粒子影响的区域,实现系统功能修复。

3.6 程序和重要数据PROM 固化

放在RAM 中的程序和数据易受SEU 的影响,可以把程序和重要数据固化在PROM 中,PROM 一般不受SEU 影响。

3.7 纠错编码抗SEU 设计

ECC(Error Correcting Code)纠错编码技术是解决SRAM FPGA 中存储区域发生SEU 错误的有效方法。根据香农理论通过增加信息的冗余位,可以有效提高数据的抗错误能力,提高信道的可靠性。因此在FPGA 数据的存储区域中通过采用纠错编码技术可以有效提高信息的传输正确性,这是解决在辐照环境下数据出现SEU 错误的有效方法。

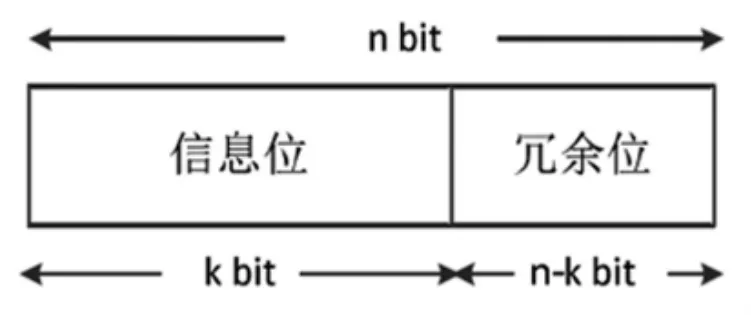

纠错编码的基本思想如图1 所示:在原有信息位的后面增加冗余位来构造一完整的信息编码字。其中k 比特位信息位,n-k 比特位冗余位一起组成n 比特编码字长。根据采用不同的纠错编码算法可以得到不同纠错性能和复杂度的编码字通常情况采用较多的纠错编码类型有:BCH 码,RS 编码,LDPC 编码等。

图1 纠错编码基本结构

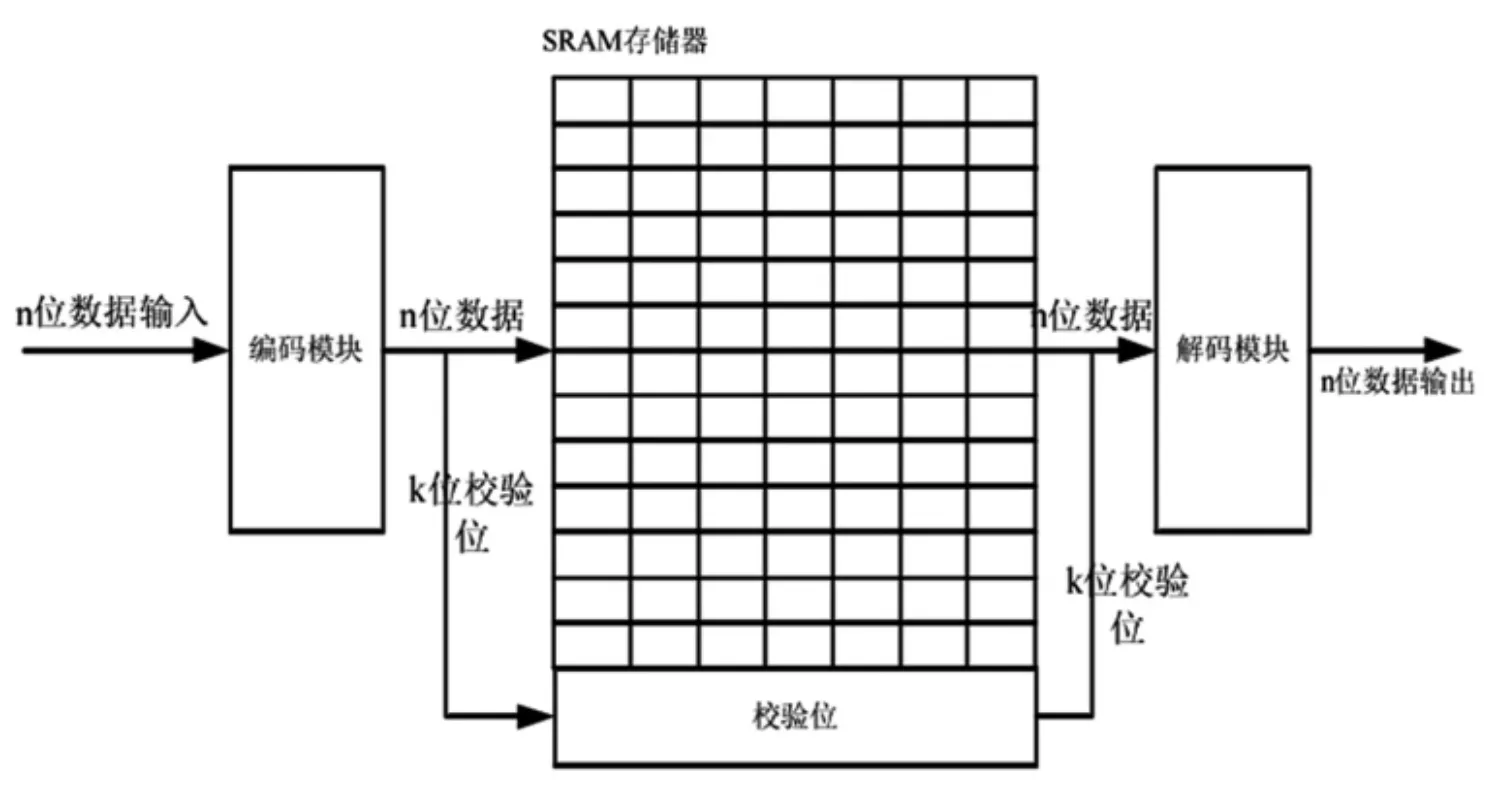

在具体电路设计中一般根据设计的预期和复杂度选用合理的编码方法。如图2 所示是一个典型的FPGA 内部数据编码存储和读取方法。其中编码数据进入FPGA内部存储区域SRAM 存储区时先进行编码,然后存在相映的存储区中,在读取时对存取的数据进行解码,如在辐照条件下,存储区中的数据发生错误,解码模块在输出时能正确恢复出原始数据,纠正因为SEU 导致的数据位错误。

3.8 状态机编码加固

对于设计中的关键状态机进行编码加固,在原有自然码、格雷码、独热码基础上可以通过增加编码冗余的方法,实现状态机加固从而能够达到检测错误甚至纠错的能力,从而避免了因为SEU 造成状态机跑飞或死锁等问题。

4 结束语

综合研究了SRAM 型FPGA 的硬件和软件可靠性设计方法,根据卫星电子设备的具体情况,选择或结合使用以上设计方法可以有效抗空间SEU。

图2 ECC 纠错一般结构