黄 玮,谢亚伟,居水荣

(江苏信息职业技术学院,江苏 无锡 214153)

流水线型构架的高速低功耗模拟数字转换器(Analog to Digital Converter,ADC),被广泛应用在图像视频处理和无线通讯等领域中,对这类ADC 来说,功耗、性噪比、精度和芯片面积等是其主要的性能指标[1-4]。

本文介绍了一种基于0.18 μm 工艺的8 位、采样速率为80 MHz 的流水线型ADC 设计中的关键技术。设计了精简且高效的数字校准和输出寄存模块,用来消除流水线型ADC 实现过程中各种因素对整个ADC性能指标的影响,提高ADC 的精度和信噪比,降低ADC 的功耗和面积,使得该ADC 特别适合作为IP 被应用在系统级芯片中,进而可以广泛应用于仪器仪表、超声系统、高分辨率图像处理和高清晰度电视等场合。

1 8 位Pipelined-ADC 整体优化设计思想

图1 是本文8 位高速低功耗流水线型ADC 的结构框图。

图1 流水线型ADC 结构框图

该流水线型ADC 包括了偏置产生、带隙基准、参考电压产生、共模电压产生、数字校准和输出寄存等外围模块以及虚线框里的转换器模块。

转换器模块是本ADC 的核心部分,主要由7 级子ADC 构成,其结构基本相似。为了减小流水线型ADC的整体功耗和面积,在第2 级至第6 级子ADC 的结构设计中采用了逐级缩放技术,在满足整体ADC 性能的情况下,后几级的开关管尺寸、电容和放大器的性能等较第1 级都有所降低。

每一级子ADC 的工作过程都是类似的。首先是对输入信号进行采样和保持,保持的信号被1.5 位快闪ADC 转换成数字信号;然后通过相乘DAC 将其转换成模拟信号,这个模拟信号与保持信号相减求余量,余量被一个运算增益放大器放大后送到下一级。当第一级子ADC 处理当前的输入信号时,第二级子ADC 处理第一级ADC 放大之后的差值,接下去每级子ADC 采用相同的方式流水线地处理。

图1 所示的流水线性ADC 结构与笔者所开发的上一代产品相比,主要是进行了以下几个方面的优化设计。

1.1 采样保持电路的优化设计

采样保持电路是流水线型ADC 的第一级,该结构在等时间间隔对模拟信号进行采样,并将采样得到信号保持供后级电路量化,从而实现流水线处理输入信号的模式,因此,采样保持电路对整个流水线型ADC的精度起到了决定性作用。

本文所介绍的ADC 中采用了如图2 所示的电容翻转采样保持电路,这种结果能够得到更低的噪声和更高的精度。

图2 电容翻转采样保持电路

通过对上述采样保持电路中的采样电容进行优化,减小了整个ADC 的功耗和芯片面积。

另外,对上述采样电路中的自举电路进行了优化设计,只使用一个电容就可以实现栅压自举开关功能,这种结构非常有利于改善整个ADC 的功耗和芯片面积。

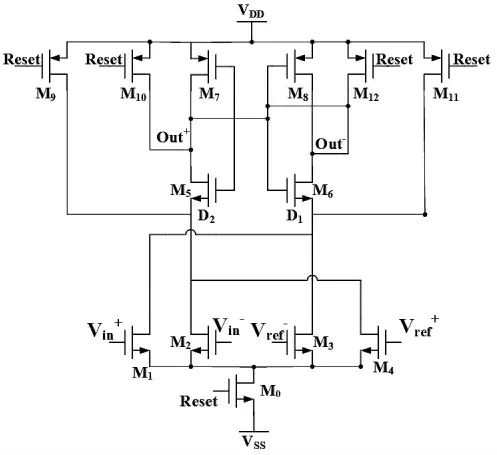

1.2 子ADC 中动态比较器的优化设计

图1 中每一级子ADC 中的动态比较器是将前一级处理输出的模拟信号量化成数字位,该比较器的设计将会影响整个ADC 的性能。

本文所介绍的ADC 对该比较器进行了优化设计,采用了图3 所示结构精简的比较器,进一步对芯片的面积减小和功耗进行了优化。

图3 结构精简的动态比较器

1.3 数字校准和输出模块的优化设计

对每一级子ADC 的输出需要经过一个数字校准和输出寄存模块,这个模块用来消除实际电路实现过程中的各种因素对整个流水线型ADC 性能的影响,从而得到在某一时刻输入所对应的高精度数字输出。上一代中,针对各级输出编码设计了延时同步和专门的数字纠错电路,没有进行级间校准的共享;另外,由于前面比较器设计方面的原因导致在数字校准前,还需要进行码型的转换,电路结构较为复杂。因此,数字校准和输出寄存模块成为流水线型ADC 设计中的一个非常重要的关键技术,对该模块的总体设计要求是电路结构要尽量简单,算法要合理,以保证整个ADC 的精度。

因此,本文将围绕这一关键技术对上一代ADC 产品进行优化设计,以提升该ADC 芯片的性能。

2 数字校准和输出寄存模块的设计

2.1 1.5 位数字校准的算法原理

本文流水线ADC 采用1.5 位每级的错位相加法进行数字校准,这种算法能最大程度地消除各子级电路比较器失调引起的非线性误差,简化数字校准电路复杂度,提高整体ADC 的精度。每级1.5 位结构只能输出00、01、10 这3 种数字码,每级在电路只需要2 个比较器,且在模数转换过程中只需由参考电压模块提供的2 个判决电平。每级1.5 位结构的输入、输出传递函数关系为[5]

式中:Vi为输入模拟信号,Vo为输出余量电压模拟信号,输出信号作为下一级的输入并继续遵循该转换曲线,Di(i=0,1,2)为不同输入信号对应的数字输出码。

根据传输函数可得每级1.5 位结构理想输入、输出转换曲线如图4(a)所示。

图4 每级1.5 位结构输入输出转换曲线

为了说明每级1.5 位结构对比较器失调影响的消除,考虑比较器失调时的非理想输入输出转换曲线如图4(b)所示,由于失调使得转换曲线的跳变电压向参考电压的两端移动,并且错误码会传递到下级并与下级的高位相加进行校准。图中本级产生两位未校准数字码(uncorrected codes),其中,低位需要与下一级校准后的高位(correction bit)相加,得到进行校准后的已校正码(corrected codes)。可以发现,只要失调电压在-Vref/4 到Vref/4 之间,数字校准电路都可以得到与两位全并行ADC 理想情况相同的数字码。

每级1.5 位算法的分析过程说明数字校准算法非常简单,图5 为本文设计的8 位流水线型ADC 对应的数字校准算法,可以看出只需要将每级的未校准数字码两两错位相加即可得到最终的正确量化数字码。误差一级一级往下传递直至最后一级的高位为止,最后一级的最后一位没有数字校准过程,因而最后子级为每级2 位的转换曲线,需要3 个比较器直接获得2 位正确的数字码。

图5 本文ADC 所采用的数字校正算法

2.2 数字校准和输出寄存模块的仿真结果

由于流水线共7 级,每级输出2 位,共有14 位输入进行错位相加,得到8 位输出数据。假如将14 位所有可能组合加到数字校准模块,观察8 位输出结果,这将是一个庞大而繁琐的工作。这里通过对整体ADC 进行瞬态仿真,其中第1 级和第2 级错位相加的情况如图6 所示。由于每级的数字校准模块都是基本单元的复制,由此可以推断整个数字校准是正确的。

图6 第1 级和第2 级错位相加仿真示意图

3 ADC 设计和实测结果

3.1 整体仿真结果及版图

以上ADC 基于0.18 μm 工艺平台设计。对整个Pipeline ADC 进行整体的瞬态仿真,仿真条件为电源AVDD=1.8 V,采样频率Fs=80 MHz,采样点数N=64,共模电压Vcm=900 mV,正参考电压Vrefp=1.275 V,负参考电压Vrefn=0.525 V。输入信号频率Fin=36.25 MHz,振幅A=1.5 V。在完成瞬态仿真后,再将理想ADC 输出进行快速傅里叶变换,结果如图7 所示。通过MATLAB软件处理数据计算得到,在输入信号频率为Fs=36.25 MHz 时,信噪比SNR 为49.9 dB,有效位数ENOB 接近8 bits。

图7 8 位ADC 频谱图

图8 为8 位Pipelined ADC 的版图,重点优化设计了采样保持电路、数字校准电路2 部分内容,核心部分面积仅为0.50 mm2。

图8 8 位流水线型ADC 的版图

3.2 实际测试结果

以上ADC 经过加工后实际测试的结果:功耗电流18 mA;在80 MHz 采样率、36.25 MHz 输入信号下,信噪比SNR 可达到49.6 dB,有效位数也可以接近8 bits。这些指标的测试过程和结果都非常稳定。

3.3 与上一代产品的对比

通过优化设计,本文中ADC 的性能指标不管是从仿真还是从实测情况看都优于作者所研发的上一代产品,主要体现在信噪比和有效位数这2 个ADC 的动态性能指标上,尤其是本次优化设计后的测试将上一代产品11.25 MHz 的输入信号频率提高到了36.25 MHz,在这种情况下,动态性能指标还能够达到较高的水平,体现了本次优化的有效性。ADC 精度的提升主要原因是采用了前端专用保持电路和栅压自举开关,另外改进了数字校准的算法和电路结构;尤其重要的是解决了上一代产品中测试结果不稳定的缺点,使得该ADC的设计具有更加明显的实用价值。

本文中ADC 经过优化后功耗也比较低,在1.8 V下,其功耗电流只有18 mA,主要因素是在优化过程中采用了结构简单的动态比较器,降低了比较器的功耗;另外,通过精确设计采样电容,也使得功耗有所降低。

最后,这个ADC的芯片面积进一步缩小,只有0.5 mm2,因为在本次优化中在数字校准部分等尽量采用结构简单的设计,使该ADC 更加适合于作为IP 被片上系统(SOC)集成电路所反复使用。

4 结论

本文介绍了一种8 位、基于0.18 μm 工艺平台、采样率为80 MHz 的高速流水线性ADC 的优化设计。在优化设计过程中,通过设计新颖的采样保持电路、合理选择电容和采用栅压自举开关,并选择合适的动态比较器电路结构,使得该ADC 具有较小的功耗和芯片面积;通过使用简化和高效的数字校准模块,使得ADC 的精度和信噪比较高,并进一步降低了芯片面积和功耗,从而使得本文中的ADC 更加适合作为SOC 中的IP 使用。